# 人工知能システムの疎結合型並列コンピュータ による高速化の研究

湯川 高志

本論文では,ルールベースシステム,ニューラルネットシステム,概念ベースシステムといった広範な応用が期待されている人工知能システムを対象として,疎結合型並列コンピュータを用いてそれらを高速化する並列化方式を提案し,それらが達成する速度向上を評価する.

人工知能システムでの処理は、処理順序の非決定性という点で、一般的な手続き型処理とは大きく異なっている.この相違点ゆえにシステムが知的振る舞いをするように見えるが,その一方で,処理量が非常に大きくシステムの動作が低速となってしまう.多くの人工知能システムでは,非決定的に処理のために,システムに入力あるいは保持された状況とあらかじめ蓄積された知識との照合処理を行っている.また,完全一致による照合のみならず,類別に基づく類似的一致を扱う場合も多い.したがって,照合と類別の各処理を高速化することにより,多くの人工知能システムにおいて全体の動作速度の向上が期待できる.本論文では,完全一致による照合処理が処理時間を支配する典型としてのルールベースシステム(プロダクションシステム;PS),パターン情報を帰納的学習によって類別処理を行うニューラルネット (NN) システム,記号情報の中でも特に自然言語情報の類似判別処理を行う概念ベースシステムを対象として,その高速化手法を論ずる.

高速化にあたっては,ヒューリスティックスによるアプローチ,専用プロセッサによるアプローチ,並列処理によるアプローチが考えられる.多くの人工知能システムではヒューリスティクスはすでに導入されており,その上での更なる高速化が要求されている.人工知能システムにおける処理の多様性を考慮すると,処理内容を限定し特化した設計を行う専用プロセッサよりも,汎用のプロセッサを多数利用する並列処理の方が,柔軟性,拡張性,経済性において優れていると考えられる.並列処理を実現する並列コンピュータは,密結合型並列コンピュータと疎結合型並列コンピュータとに大きく分類されるが,10以下の並列度を主眼においた密結合型よりも,中~高並列でのスケーラブルな性能を期待できる疎結合型並列コンピュータの方が,大幅な高速化を期待する本論文の目的に適していると言える.

本論文では,以上の議論に基づき,ルールベースシステム,ニューラルネットシステム,概念ベースシステムのそれぞれに対し,疎結合型並列コンピュータ上で並列処理することにより処理を高速化する手法を提案し,それらの速度向上度を評価している.

ルールベースシステムに対しては,条件照合に用いられるRETEマッチ・アルゴリズムについて,その特性を解析的に分析し,種々の並列化軸について高速化の可能性を議論する.その議論に基づいてバス結合型並列コンピュータに好適な並列化方式である"TWIN方式"を提案する.TWIN方式を効率的に処理する機能をバスに備えた並列コンピュータ"Presto"の設計・製作とシステムの実装を行い,実験評価の結果を示す.

ニューラルネットシステムに対しては,最も多くの処理時間を占めるバックプロパゲーション (BP) 学習について,その処理を連続行列演算として定式化し,並列化に際しての速度向上の上限値を理論的に導出する.疎結合型並列コンピュータに対する並列化方式を提案し,それら方式が理論的な上限値を達成していること,すわなち最適並列化方式であること示す.

概念ベースシステムでは,類似概念検索処理に対して,探索空間を絞り込みつつバス結合型並列コンピュータにより並列処理する方式を提案する.更に,自然言語処理に好適な意味ネット向け並列コンピュータ SNAP(Semantic Network Array Processor)を用いた並列処理方式を提案し,処理がスケーラブルでありプロセッサ数に応じてリニアな速度向上が得られることを示す.

近年の状況として、インタネット上での溢れんばかりの情報・知識の洪水から知識を抽出・構成するために高速な人工知能システムが必要とされる事、コモデティ・ハードウェアを用いた疎結合型並列コンピュータが実現されコストパフォーマンスが大幅に上昇している事について述べ、本研究が、情報処理技術の今後の発展に資するであろうことをもって結言とする.

# 目次

| 第1章 | 序論    |                                                | 1  |

|-----|-------|------------------------------------------------|----|

| 1.1 | 研究の   | 自的                                             | 1  |

| 1.2 | 研究の   | 動機と主な成果                                        | 2  |

|     | 1.2.1 | プロダクションシステムの並列化                                | 4  |

|     | 1.2.2 | ニューラルネットシステムの並列化                               | 5  |

|     | 1.2.3 | 類似概念検索の並列化・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 5  |

| 1.3 | 本論へ   | 、の準備                                           | 6  |

|     | 1.3.1 | 並列コンピュータとその分類                                  | 6  |

|     | 1.3.2 | 本研究が対象とする並列コンピュータ                              | 12 |

| 第2章 | プロタ   | 「クションシステム条件照合の並列化                              | 14 |

| 2.1 | プロダ   | 「クションシステムと RETE マッチ・アルゴリズム                     | 15 |

|     | 2.1.1 | プロダクションシステム                                    | 15 |

|     | 2.1.2 | 認知–実行サイクル                                      | 20 |

|     | 2.1.3 | RETE マッチ・アルゴリズム                                | 22 |

| 2.2 | プロダ   | ・<br>「クションシステム高速化手法                            | 25 |

| 2.3 | 条件照   | 合処理の並列性と従来の並列化方式                               | 27 |

| 2.4 | RETE  | ネットワークのモデル化による並列化方式の評価                         | 31 |

|     | 2.4.1 | エキスパートシステムの問題特性                                | 32 |

|     | 2.4.2 | RETE ネットワークのモデル化                               | 33 |

|     | 2.4.3 | RETE <b>ネットワークの諸特性</b>                         | 35 |

|     | 2.4.4 | 速度向上度の推定式・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・  | 40 |

|     | 2.4.5 | 各並列化方式の解評価析と考察                                 | 43 |

| 2.5 | TWIN  | -<br>「方式の提案                                    |    |

|     | 2.5.1 | 2 入力ノードに関する考察                                  |    |

|     | 2.5.2 | 2 入力ノード処理の並列化                                  |    |

|     | 2.5.3 2入力ノードの連鎖の並列化          | 52 |

|-----|------------------------------|----|

|     | 2.5.4 TWIN 方式                | 53 |

| 2.6 | TWIN 方式の解析的評価                | 55 |

| 2.7 | 実験による評価                      | 55 |

| 2.8 | まとめ                          | 57 |

| 第3章 | プロダクションシステム向け並列コンピュータ Presto | 59 |

| 3.1 | 認知-実行サイクルの並列化方式              | 60 |

| 3.2 | ルール・WME の割り付け法               | 62 |

|     | 3.2.1 RETE <b>サブネットの割り付け</b> | 62 |

|     | 3.2.2 WME <b>の割り付け</b>       | 63 |

|     | 3.2.3 アクション部の割り付け            | 65 |

| 3.3 | PS 向け並列コンピュータ Presto         | 65 |

|     | 3.3.1 全体構成                   | 65 |

|     | 3.3.2 プロセッシングエレメント (PE)      | 67 |

|     | 3.3.3 バスの機能                  | 69 |

| 3.4 | 推論インタプリタの実装                  | 73 |

|     | 3.4.1 フェーズ移行処理               | 74 |

|     | 3.4.2 同期処理                   | 74 |

|     | 3.4.3 グローバル競合解消プロセッサの決定法     | 75 |

|     | 3.4.4 認知-実行サイクルを通した動作        | 76 |

| 3.5 | システムソフトウェア                   | 77 |

| 3.6 | 性能評価と考察                      | 77 |

|     | 3.6.1 ベンチマーク ES による実験        | 78 |

|     | 3.6.2 経路探索 ES による総合性能評価      | 80 |

|     | 3.6.3 8 クイーン問題による評価          | 83 |

| 3.7 | まとめ                          | 84 |

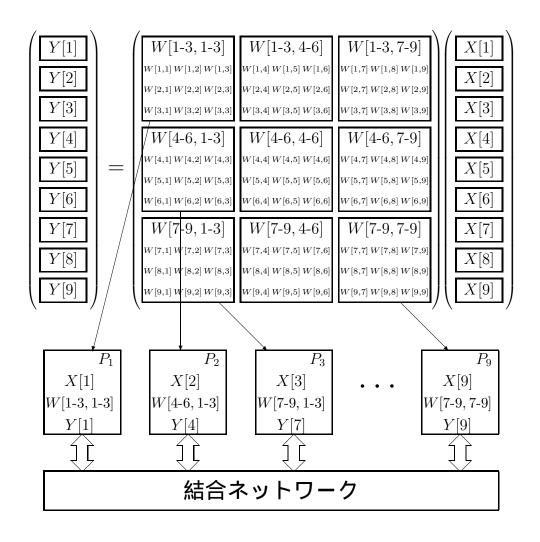

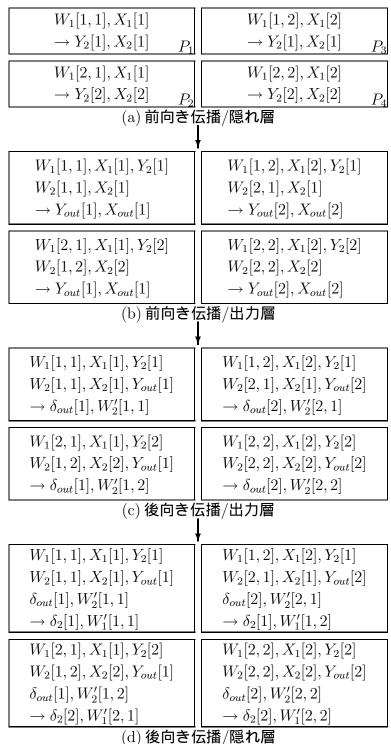

| 第4章 | ニューラルネットシステムの並列化             | 86 |

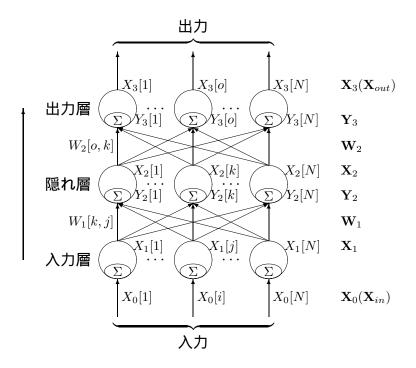

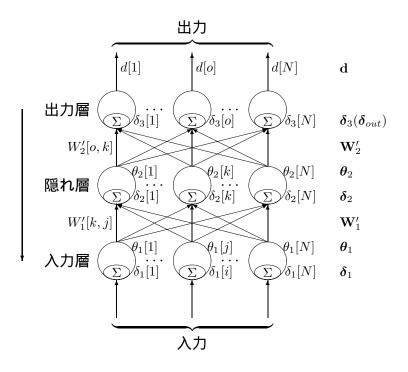

| 4.1 | 多層ニューラルネットとバックプロパゲーション       | 87 |

|     | 4.1.1 記号の定義                  | 87 |

|     | 4.1.2 前向き伝播                  | 89 |

|     | 4.1.3 後向き伝播                  | 91 |

| 4.2 | 従来の   | )バックプロパゲーション並列化方式 92                        |

|-----|-------|---------------------------------------------|

| 4.3 | 連続行   | f列演算の並列化における通信量と計算量の下限値93                   |

|     | 4.3.1 | 連続行列演算の並列処理94                               |

|     | 4.3.2 | 通信ステップ数と演算ステップ数の定式化 95                      |

|     | 4.3.3 | 通信ステップ数と演算ステップ数の下限値100                      |

| 4.4 | BP 並  | 列化における通信ステップ数の下限値103                        |

|     | 4.4.1 | BP における連続行列演算の特性                            |

|     | 4.4.2 | BP における通信ステップ数の下限値 106                      |

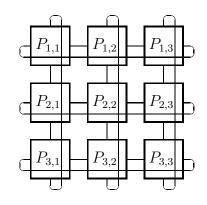

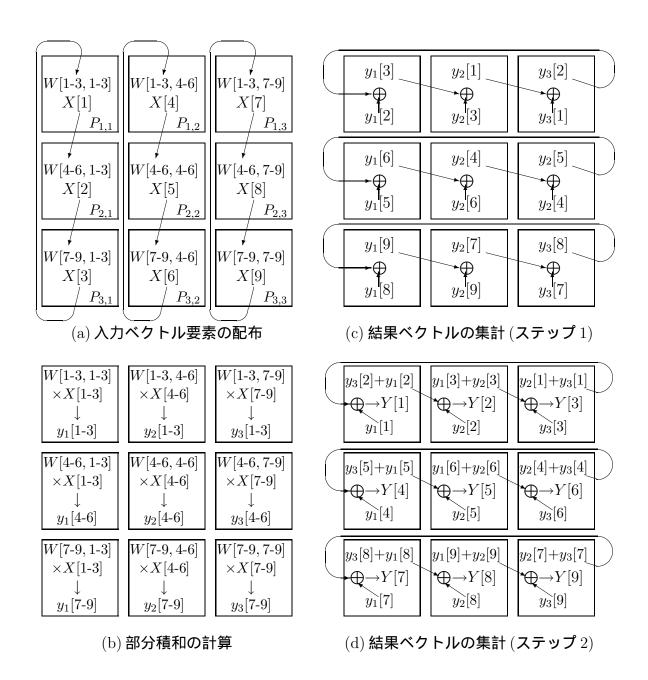

| 4.5 | 2 次元  | アレイ型並列コンピュータ向けの並列化方式109                     |

|     | 4.5.1 | 並列化方式110                                    |

|     | 4.5.2 | 通信ステップ数の最小化                                 |

|     | 4.5.3 | 従来方式との比較                                    |

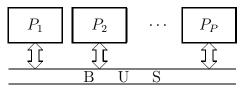

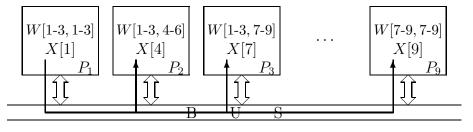

| 4.6 | バス緑   | 結合型並列コンピュータ向けの並列化方式 $\dots\dots\dots$ $114$ |

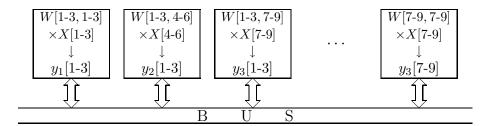

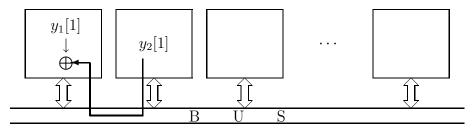

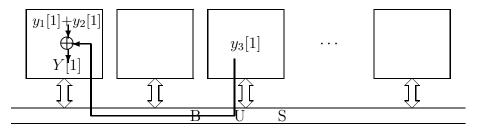

|     | 4.6.1 | 並列化方式114                                    |

|     | 4.6.2 | 通信ステップ数の最小化                                 |

|     | 4.6.3 | 従来方式との比較                                    |

| 4.7 | まとめ   | <b>)</b>                                    |

| 第5章 | 類似相   | 既念検索の並列化 120                                |

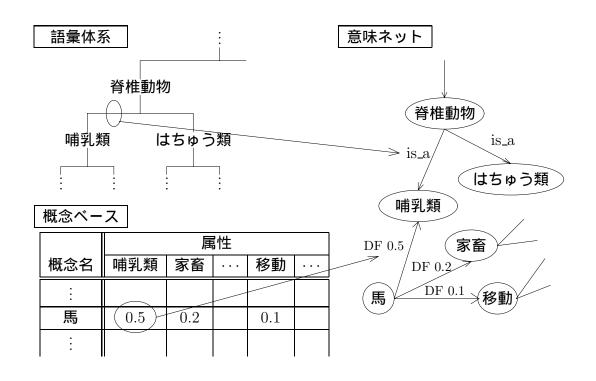

| 5.1 | 概念の   | )類似判別と検索                                    |

|     | 5.1.1 | <b>観点に基づく類似判別</b>                           |

|     | 5.1.2 | 概念ベース                                       |

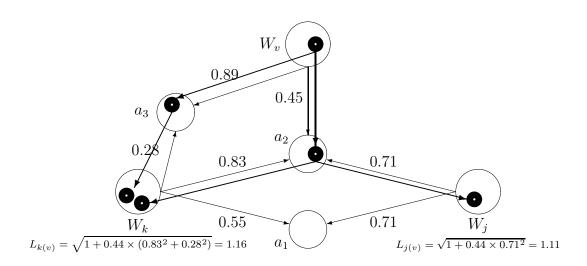

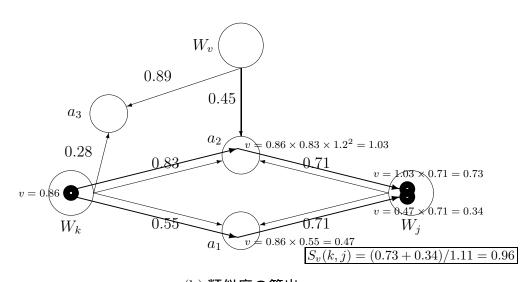

|     | 5.1.3 | 類似度計算アルゴリズム                                 |

|     | 5.1.4 | 類似概念検索の基本的方式                                |

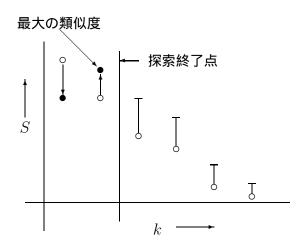

| 5.2 | バス緑   | 告合型並列コンピュータによる類似概念検索の高速化126                 |

|     | 5.2.1 | 類似度の上界127                                   |

|     | 5.2.2 | 探索空間削減する類似概念検索アルゴリズム 129                    |

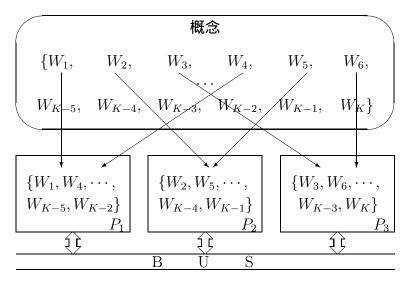

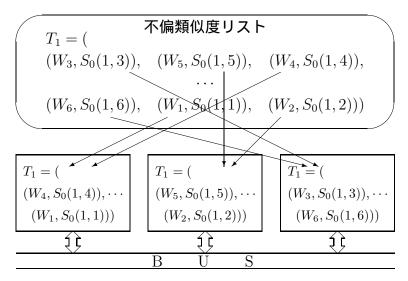

|     | 5.2.3 | バス結合型並列コンピュータ向け並列化方式 131                    |

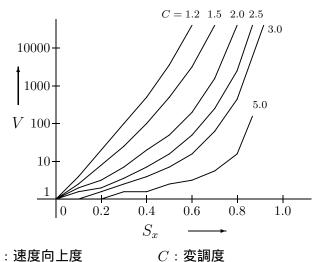

|     | 5.2.4 | 解析的性能評価                                     |

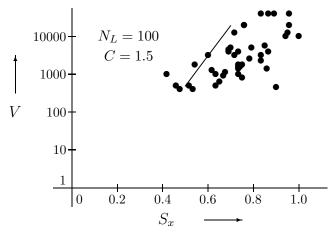

|     | 5.2.5 | 実験評価                                        |

| 5.3 | SNAP  | ー<br>による類似概念検索の並列化                          |

|     | 531   | マーカ伝播モデルと SNAP アーキテクチャ 130                  |

| 第6章 |       |         |     |     | • • | <br> | <br> | <br>146   |

|-----|-------|---------|-----|-----|-----|------|------|-----------|

| 5.4 | まとめ   |         |     |     |     |      |      | 144       |

|     | 5.3.3 | 類似判別方式  |     |     |     | <br> | <br> | <br>. 140 |

|     | 5.3.2 | 概念ベースの意 | 味ネッ | ト表現 | ₹.  | <br> | <br> | <br>. 139 |

# 図目次

| 2.1  | プロダクションシステムの構成                               | 16 |

|------|----------------------------------------------|----|

| 2.2  | RETE ネットワークの概念図                              | 23 |

| 2.3  | 2 入力ノードでの処理                                  | 25 |

| 2.4  | 2 入力ノードの連鎖                                   | 28 |

| 2.5  | RETE マッチ・アルゴリズムの並列化方式                        | 31 |

| 2.6  | 2 入力ノードのモデル                                  | 35 |

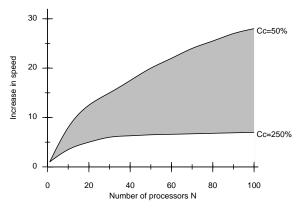

| 2.7  | 解析評価による速度向上特性                                | 46 |

| 2.8  | 速度向上の問題依存性                                   | 47 |

| 2.9  | 2 入力ノード処理の並列化                                | 52 |

| 2.10 | TWIN 方式の構造並列化                                | 54 |

| 2.11 | TWIN 方式の解析評価結果                               | 56 |

| 2.12 | 実験システムの構成                                    | 56 |

| 2.13 | 実測結果                                         | 57 |

| o 1  | ★되/사회전에 보고 시                                 | 60 |

| 3.1  | 並列化認知サイクル                                    |    |

| 3.2  | WME <b>操作</b>                                | 64 |

| 3.3  | Presto <b>のハードウェア構成</b>                      | 66 |

| 3.4  | ホストプロセッサに接続された Presto                        | 66 |

| 3.5  | Presto の PE 基板 (1 枚あたり 2PE)                  | 67 |

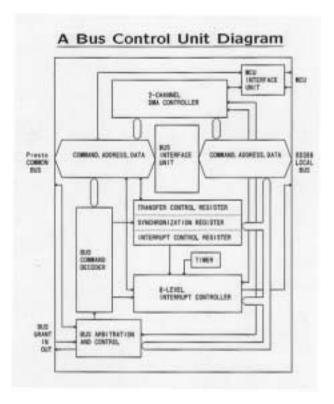

| 3.6  | BCU のブロックダイヤグラム                              | 69 |

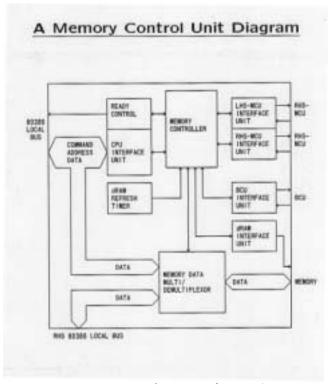

| 3.7  | MCU のブロックダイヤグラム                              | 70 |

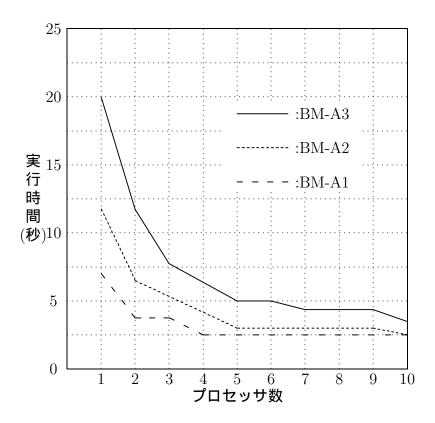

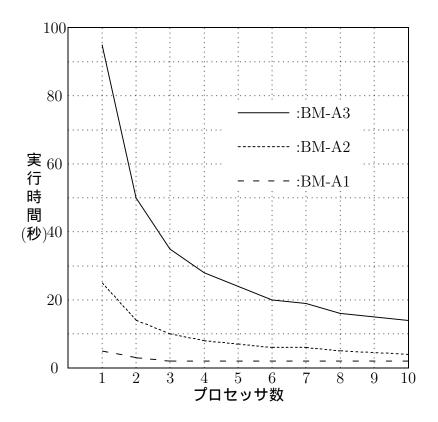

| 3.8  | トップノード並列化方式でのベンチマーク結果                        | 79 |

| 3.9  | TWIN 方式でのベンチマーク結果                            | 80 |

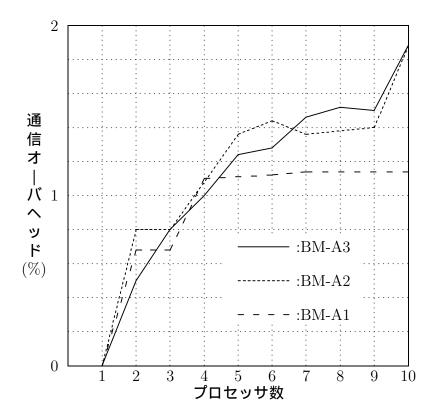

| 3.10 | 通信オーバヘッド・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 81 |

| 3.11 | 各フェーズの実行時間比                                  | 81 |

| 3.12 | 競合解消/実行フェーズ処理時間の変化                           | 83 |

| 4.1 | 多層ニューラルネット (前向き伝播)                   |

|-----|--------------------------------------|

| 4.2 | 多層ニューラルネット (後向き伝播)                   |

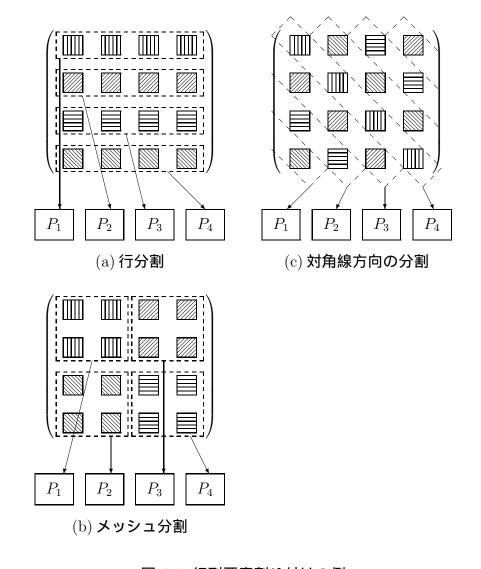

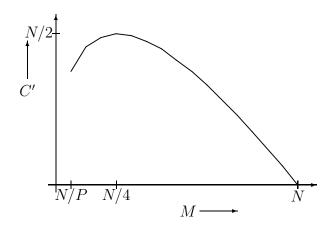

| 4.3 | 行列要素割り付けの例96                         |

| 4.4 | M に対する $C'$ の変化                      |

| 4.5 | 通信・演算ステップの下限値を与える行列・ベクトルの割り付け法 $104$ |

| 4.6 | BP <b>並列演算の例</b>                     |

| 4.7 | 並列アーキテクチャ109                         |

| 4.8 | 二次元アレイ向けの最適並列化111                    |

| 4.9 | バス結合向けの最適並列化                         |

| 5.1 | 探索空間の絞り込み130                         |

| 5.2 | バス結合型並列コンピュータ向け類似概念検索方式の概念割り付け 133   |

| 5.3 | UB-FSR <b>の速度向上度推定値</b>              |

| 5.4 | 実験結果                                 |

| 5.5 | 概念ベースの意味ネットによる表現                     |

| 5.6 | SNAP <b>による類似度計算</b>                 |

# 表目次

| 2.1 | RETE ネットワークの構造を支配する問題特性パラメータ                         | 33  |

|-----|------------------------------------------------------|-----|

| 2.2 | RETE ネットワークの動作を支配する問題特性パラメータ                         | 34  |

| 2.3 | RETE <b>ネットワークの構造的特性</b>                             | 40  |

| 2.4 | RETE <b>ネットワークの処理量特性</b>                             | 40  |

| 2.5 | 並列化方式と好適なアーキテクチャ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 43  |

| 2.6 | 速度向上度推定式の項の値・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・      | 44  |

| 2.7 | 評価に用いた ES 特性                                         | 45  |

| 3.1 | ベンチマーク ES                                            | 78  |

| 3.2 | 負荷ばらつき係数                                             | 82  |

| 3.3 | 8Queen 問題の処理時間 (4PE の場合)                             | 84  |

| 4.1 | プロセッサへの要素の割り付け                                       | 106 |

# 第1章 序論

### 1.1 研究の目的

情報処理技術が浸透し社会を構成するに欠くべからず要素になるとともに,データ通信ネットワーク技術の発展により地球規模での高速・高度な情報流通が実現しつつある.このような高度情報流通社会においては,人間が快適かつ容易に情報を扱うために,また,大量に流通する情報からユーザにとって必要な情報を的確に捕捉し処理するために,知的な情報処理が求められる.このような背景から,人間の思考過程や認識過程をコンピュータで模擬することにより知的情報処理を実現する人工知能システムが多く研究されている.

人工知能システムには、その動作原理上、従来のコンピュータで実行するとその処理速度が非常に低速になってしまうものが多く存在する.しかしながら、従来のコンピュータの柔軟性、これまでの技術的蓄積、市場規模を背景とした今後の性能的発展を鑑みると、まったく動作原理の異なる人工知能システム専用のコンピュータを新たに創造して従来のコンピュータを上回る性能を実現するのは容易なことではない、従来のノイマン型コンピュータの動作原理を踏襲しつつ、人工知能システムを高速化するためには、多数のプロセッサを用いて処理を並列化することが考えられる.

本研究の目的は,並列コンピュータを用いて人工知能システムの高速化を図る ことにある.

並列化のアプローチは,更に,専用プロセッサと専用の相互結合網を用いるアプローチ,汎用プロセッサに専用相互結合網を用いるアプローチ,汎用プロセッサを用い相互結合網も汎用部品を流用するアプローチなどに細分される.このうち汎用プロセッサを用いるアプローチでは,従来型のコンピュータに対する技術的発展のほとんどをそのまま享受することが可能である.相互結合網は,並列化に際してはその性能の支配的要因となり得るため,アプリケーションとなる人工知能システムに適した形態とする必要があることは当然として,更にプロセッサの

性能向上に追従したデータ転送性能が必要とされる.相互結合網に汎用部品を流用するアプローチでは,多くの汎用部品がプロセッサの発展と共に性能が向上しているため,その性能向上をそのまま享受できる.一方,専用型では常に開発投資が必要となり,プロセッサ技術の進歩に追従できるとは限らないが,構成が比較的単純な直接網に限れば,LSI技術や回路技術の進歩に関しては少なくともプロセッサと同様にその恩恵を享受することができる.以上のことから,汎用プロセッサを,汎用部品を流用した相互結合網または専用設計の直接網により相互接続した疎結合型並列コンピュータを用いることにより,一般のコンピュータ技術の発展に追従することができ,性能的にも常に優位性を保持できると期待される.そこで,本研究では,人工知能システムを疎結合型並列コンピュータによって並列処理し,実用的な処理速度を得ることをねらう.

## 1.2 研究の動機と主な成果

本論文では,広範な応用がなされており,今後も更なる応用が期待される人工知能システムに対し,疎結合並列コンピュータによる並列化方式を提案する.本論文が対象としたシステムは以下の通りである.

#### 1) ルールベースステム

ルールベースシステムは,人間が外界の状況を認知し,認知結果に適合する行動を起こす過程に基づいたシステムであり,これまで,専門家の判断を模擬するエキスパート・システム(ES)の推論メカニズムとして多く用いられてきた.近年では,人間が協調して知的作業を行う過程を模擬したマルチエージェント・システムへの適用も期待されている.

ルールベースシステムに用いられる推論メカニズムがプロダクション・システム (PS) である.PS は条件照合・競合解消・実行の3フェーズから成る認知―実行サイクルを繰り返すことにより推論を行う.PS において実行すべき命令は,サイクルごとの条件照合および競合解消によって決定される.すなわち非手続き型処理の典型である.このうち条件照合フェーズでは,すべてのルール条件部に対し,その時点でのすべてのデータの照合が行われるため,処理量が非常に大きく,システムとしての処理速度が低速となる.

本研究では、まず処理時間を支配する条件照合フェーズの並列化方式を検討し、

次にそれをベースとして,認知-実行サイクル全体を通じた並列化方式について検 討する.

#### 2) ニューラルネット (NN) システム

NNシステムは生物の神経回路網を模擬したシステムであり,図形認識や音声認識をはじめ様々なパターン識別に多く用いられている.これまでの統計的なアプローチや記号処理的アプローチでは十分な識別能力が得られない対象に対しても,NNシステムを用いることにより良い識別結果が得られる場合も多い.NNシステムでは,パターン識別を正しく行うために,入力と正答との組を多数提示することで学習を行う.この例示学習のためのアルゴリズムとしてバックプロパゲーション(BP)がもっとも一般的に用いられている.BPは,入力から計算した結果と提示された正答との差分をNNシステム内で伝播させつつ,NNの結合係数を微少変化させることにより学習を行う.この例示とそれに基づく結合係数の微少変化を多数回繰り返すことにより,結合係数が次第に収束し,識別能力の高いシステムとなる.BPでは,例示を多数(数万から時には数百万)回繰り返すことにより学習を行うため,学習に非常に多くの時間がかかる.

BPの処理は,行列演算の繰り返しとそれに基づく行列要素への操作として定式化できる.行列演算であることから並列化に際しては,負荷を均等とすることは容易であると考えられる.となれば,総計算量の増加(分割損)と通信オーバヘッドがその性能を左右することになろう.本研究では,BP並列化における総計算量と通信量とを定式化し,その理論的下限値とそれを得るための条件とを検討する.また,それに基づいて並列化方式を考案する.

#### 3) 概念ベースシステム

概念ベースシステムは、人間が持つ日常的な単語に関する知識ベースであり、単語間の包含関係や類似関係を判別するシステムである。World Wide Web(WWW)の検索システムとして、テキスト内容に指定した検索語が含まれているか否かに基づいてスコアリングする全文検索システムが発展してきているが、今後は、指定した語そのものだけではなく、それに類似した語もスコアの対象とする類似検索が必須となって来よう。このような検索システムには、類似語の判別のために概念ベースが必須となる。また、検索のみならず、文章の要約や知識が欠落していた場合に類似知識から補って推論を行う補完推論等、概念ベースは広範な応用

が期待されている、概念ベースの基本的な機能である類似概念検索は,ある概念が与えられた際に,概念ベースに含まれる全概念の中からもっとも類似した概念を探しだす機能である、概念ベースには,日常的に用いられる数万~数十万の概念が含まれているため,類似概念検索では,これらにすべてに対して類似度を計算する必要があり,非常に時間がかかる処理となっている.

本研究では,並列処理による類似概念検索の高速化を検討する.上述のとおり概念数が非常に大きいため,実用的な速度を得るには,全探索という原始的な方法に対して数千~数万倍の高速化が必要とされる.本研究では,探索空間を絞り込みつつ中並列の並列化でこれを達成するアプローチと,スケーラブルな並列化方式を考案して高並列コンピュータによりこれを達成するアプローチの両者を検討する.

以下,それぞれについて,本研究での成果を述べる.

#### 1.2.1 プロダクションシステムの並列化

バス結合型並列コンピュータに向けた PS の並列化方式を提案し,解析的に性能を評価して他の方式と比較した.提案した並列化方式 "TWIN 方式"は,条件照合に用いられる RETE マッチ・アルゴリズムの持つ制御流れの並列性(構造的並列性)とデータ処理の並列性を巧妙に組み合せることにより,通信オーバヘッドと負荷ばらつきとの両者を小さく抑えた方式である.本方式により,低廉に構築可能なバス結合型並列コンピュータにおいても安定的に性能が得られる.

性能評価においては,実際にプログラムを実装することなく並列化時の性能を推定できれば,多くの並列化方式を同一条件下で検討・比較できる.このために解析的性能評価手法を提案している.本評価手法では,RETE マッチ・アルゴリズムに用いられる RETE ネットワークをモデル化し,そのモデルに基づいて,並列化時の速度向上度を計算によって求める速度向上推定式を構築した.本手法を用いれば,PSのアプリケーション・プログラムにあたるエキスパート・システム(ES)の特徴パラメータと並列化方式とから,速度向上度を計算により推定することができる.この速度向上推定手法によって TWIN 方式と既存の代表的な並列化方式を評価し比較した.

さらに,提案したTWIN方式を実装するのに適したバス結合型並列コンピュータ "Presto" と, PS の推論インタプリタ全体を通じた並列化方式を提案している.

Presto は,低廉に構築できるバス結合型並列コンピュータであるが,TWIN 方式をより効率的に実装するために,放送,同期,プロセッサ間割込を実現する機構をバスに持たせている.PS では照合が処理時間の大部分を占めるとはいえ,10 倍を越える速度向上を得るには,推論の認知—実行サイクルを構成する他のフェーズ,すなわち競合解消フェーズと実行フェーズも並列化する必要がある.このために,TWIN 方式による照合並列化を基本とした,PS 推論全体の並列化方式を提案している.更に,NTT で開発された KBMS 推論インタプリタをこの並列化方式に基づいて Presto 上に実装し,性能を評価している.

#### 1.2.2 ニューラルネットシステムの並列化

BP学習の並列処理について論じ、バス結合型並列コンピュータと2次元アレイ型並列コンピュータとに対する並列化方式を提案した.また、BP並列化に際しての本質的な処理量および通信量について考察し、理論的な下限値とそれを実現するための条件(最適並列化条件)とを明確にした.更に、提案方式のうち2次元アレイ型並列コンピュータに対する方式が、ここで明らかにした最適並列化条件を満足していること、すなわち計算量・通信量が本方式よりも小さい並列化方式は存在しないことを示した.また、バス結合型並列コンピュータする方式では、従来方式の通信量がプロセッサ数に比例していたのに対し、それをプロセッサ数の平方根オーダに抑えることができた.

### 1.2.3 類似概念検索の並列化

類似概念検索に対する並列化方式としてバス結合型向けの並列化方式と意味ネット並列マシン向けの並列化方式とを提案した.バス結合型向けの方式は,類似度計算法の特性を利用して見込みのない概念に対する類似度計算を省くとともに,バス結合型並列コンピュータによって処理を並列化する.これにより,原理的な検索方式に対して1万倍台の速度向上が得られる.意味ネットマシン向け方式は,意味ネット並列マシンSNAP(Semantic Network Array Processor)上に概念ベースをマッピングして,類似度計算を高並列化できるスケーラブルな並列化方式である.

## 1.3 本論への準備

#### 1.3.1 並列コンピュータとその分類

コンピュータに用いられるプロセッサの処理速度は,LSI技術,特に微細加工技術の進歩に支えられて,これまで長足の進展を遂げてきた.しかしながら,現在主流である CMOS プロセスも,速度的な面では,さほど遠くないうちに限界を迎るであろうと予測されている.また,それに代る GaAS やジョセフソン素子等は,消費電力,集積度,歩留りなどの面で未だに多くの問題を抱えており,近い将来に CMOS に取って代わる技術にはなりそうにない.

単一のプロセッサでの速度の限界を突破するために,多数のプロセッサを用いてひとつのアプリケーションを並列に処理する技術が古くから研究されてきた.アプリケーション・プログラムを適切に複数の部分(処理単位)に分割し,複数のプロセッサでそれぞれの処理単位を実行すれば,単一プロセッサで実行する場合よりも短い時間で結果を得ることができる.このような並列処理を行うことを目的として構成されたコンピュータが並列コンピュータである.しかしながら,並列コンピュータと一口に言っても,扱う処理単位の細かさ(粒度),命令とデータの流れとの関係,プロセッサ間のデータ交換の方法などによって,その構成には非常に広範なバリエーションがある.そこで,本節では,並列コンピュータの分類 [92] を示し,そのうち MIMD 型マルチコンピュータを更に共有メモリ型 (密結合型) と分散メモリ型 (疎結合型) とに分類する.

コンピュータ・アーキテクチャは,機械命令の起動形態によってコントロール駆動型,データ駆動型,要求駆動型に分類できる.また命令とデータの流れにより,SISD(single instruction single data stream)方式,SIMD(single instruction multi data stream)方式,VLIW(very long instruction word)方式,演算パイプライン(arithmetic pipeline)方式,MIMD(multi instruction multi data stream)方式に分類できる.データ駆動型と要求駆動型では必然的にMIMD方式になる.これらは非ノイマン型並列コンピュータと呼ばれる.コントロール駆動型はあらゆる方式を取り得るが,SISD方式が従来の単一プロセッサのコンピュータに相当する.他の方式をとるものはノイマン型並列コンピュータと呼ばれる.コントロール駆動型での各方式について,以下にその概要と特徴を述べる.

#### SISD 方式

SISD 方式では、演算装置を一つ持ち、一つの機械命令の実行によって一つの

演算結果が得られるもので,並列コンピュータとしての分類には含まれない. 汎用コンピュータが SISD 方式の代表である.また近年,高級言語コンピュータが開発されているがこれも SISD 方式に分類される.高級言語コンピュータは,高級言語のソースコードを直接,あるいは抽象度の高い中間形式に変換して,ハードウェアにより処理するもので,1ステップあたりの処理が複雑な人工知能向け言語を対象としたものが多く開発されて来た[30,36,49]. しかしながら,市場規模の圧倒的に大きな汎用プロセッサへの開発投資の集中によって,現在では,高級言語向け専用コンピュータの性能的優位性は失われている.

#### SIMD方式

SIMD 方式は,演算装置を多数持ち,それらが一つの制御部から発せられた演算命令を同時に実行する.演算装置は結合網を介して互いに接続されている.すべての演算装置が同一の命令により駆動されるため,処理方法が単一なデータが多数ある場合にその真価を発揮する.ベクトルや配列等に対する演算を必要とする分野に適しており,科学技術計算,画像処理,信号処理,データ・サーチ,パターン・マッチング,連想処理などに利用できる.

人工知能を応用対象とした SIMD 方式並列コンピュータの代表的なものとして,Connection Machine [33] があげられる.Connection Machine は 1 ビットの演算器と 4k ビットのメモリから構成されるプロセッシング・エレメント (PE:processing element; セルとも呼ぶ)を 2 進 n- キューブ網で結合したものであり,集合演算,木構造演算,バタフライ演算,文字列演算,サーチ,配列演算などを高速に処理できるとされている.

#### VLIW 方式

VLIW 方式は,水平型マイクロプログラムから派生した方式であり,語長の 非常に長い機械命令を多数のフィールドに分割し,個々のフィールドで演算 器やメモリを独立に制御する方式である.長形式の命令に同時実行可能な 演算が埋め込まれてその性能を発揮することができる.この演算の埋め込み はコンパイラによって行われるので,コンパイラ技術が重要となる.並列性 の抽出をコンパイラで行う分,実行時の並列制御は簡単となるため,ハードウェア構成は単純となり高速化を達成できる.

#### 演算パイプライン方式

演算パイプライン方式では,演算装置が多数のステージから構成されており,データを流れ作業の原理で処理する.最初のデータが入力されてから最初の結果がでるまでは時間がかかるが,それ以降は連続的に結果が得られる.各ステージでの処理時間が等しく,データが十分に大量であればステージ段数に等しい速度向上が得られる.ベクトルや配列に対する演算を高速に実行するスーパ・コンピュータでは主流の方式である.

#### MIMD 方式 (マルチプロセッサ方式)

コントロール駆動型の MIMD 方式は,プロセッサを相互結合網により複合 した形態である.プロセッサは,それぞれが演算器や制御部を持ち,自律的 に動作できる.このため,マルチプロセッサ方式とも呼ばれる.

次節で述べるように,主記憶の位置により,それを共有する共有メモリ型(密結合型),個々のプロセッサが独自に主記憶を持ちメッセージ交換によりデータをやり取りする分散メモリ型(疎結合型)に分られる.また,相互結合網も,直接網と間接網に分類でき,更に同一分類中にも多くのトポロジーが考えられる.この相互結合網は,並列コンピュータのコストと性能とを左右する.また,適用分野もこれに依存する.

このようなことから,適用分野が比較的明確で限定的な他の方式に比べて,マルチプロセッサ方式は,様々な適用分野が考えられ,また,それぞれの分野で様々な相互結合網の形態に対する並列化アルゴリズムが研究されている.人工知能向けとしても多く開発されており,DADO[21],Non Von などが代表的なものとしてあげられる.DADOは,木構造の分散メモリ型並列コンピュータであり,この上で PS 等の人工知能システムが実装されている.次節では,本方式についてより詳しく述べる.

#### 密結合型並列コンピュータと疎結合型並列コンピュータ

MIMD 方式 (マルチプロセッサ方式) は,演算装置と制御部からなるプロセッサを相互結合網により多数結合した方式である.プロセッサに命令やデータを供給する主記憶の配置によって,密結合型(共有メモリ型)と疎結合型(分散メモリ型)に分類される.

密結合型並列コンピュータでは,各プロセッサが主記憶装置を共有して動作す

る.プロセッサからは共有されている主記憶領域がメモリ空間上に直接見えることになり、これを命令の記憶領域としてもデータの記憶領域としても利用することができる.主記憶がすべてのプロセッサから共有されるため、主記憶装置に対するアクセス・トラフィックが大きくなり、プロセッサ数が増加するとここにボトルネックが生じて性能が低下する.これを避けるために、他のプロセッサとはアクセスが競合しないローカル・メモリを備えているものも多い.また、プロセッサやそれの群ごとにキャッシュ・メモリを装備する場合もある.この場合にはキャッシュ・コンシステンシの制御が重要となる.

プロセッサと主記憶装置の結合は、単一バス結合が最も一般的であるが、階層バス結合やクロスバ結合を採用したものもある。いずれの場合も、共有メモリへのアクセス競合によってその性能が抑えられるため、一般にプロセッサ数が少ない領域で使われる。汎用大型機の双頭プロセッサ、UNIX サーバや PC サーバにおける SMP(symmetric multi processor) 等が代表的である。

疎結合型並列コンピュータは、個々のプロセッサが自身の主記憶 (ローカルメモリ)を持ち独立した1台のコンピュータとして動作する.このため、これをマルチコンピュータ方式とも呼ぶ.プロセッサ間のデータ交換は入出力ポート等を通じ、相互結合網を介してメッセージ通信の形式で行われる.後述するようにプロセッサを結合する相互結合網には様々な方式が考案されている.相互結合網のトポロジにも依存するが、一般に多数のプロセッサによって構成することが可能であり、数10台~数万台規模の並列コンピュータが開発されている.

密結合型並列コンピュータでは、自プロセッサ内でのデータへのアクセスも、プロセッサ間でのデータの交換も、プロセッサから見ればともにメモリアクセスであるため、プログラムは容易である反面、メモリ・アクセス競合等のオーバヘッドが予測しにくい、一方、疎結合型並列コンピュータでは、自プロセッサ内に閉じたアクセスと他のプロセッサとのデータ交換は、プロセッサにとって全く異なった動作であり、プログラマが明確に意識することになる、このため、アルゴリズムの並列化は、分割による処理量の増加、通信オーバヘッド、プロセッサの負荷ばらつき等を十分に考慮し注意深く行う必要がある、その反面、性能があらかじめある程度予測可能であり、並列化にあたっても実際にプログラムを実装することなく様々な方式を検討することができる、また、良い並列化方式を見つけることができれば高性能を安定に達成できる、このようなことから、本論文では、疎結合型並列コンピュータを用いた人工知能システムの並列化方式を論ずる、

次節では,疎結合型並列コンピュータを相互結合網に着目して分類し,本論文 が対象とするアーキテクチャについて述べる.

#### 疎結合型並列コンピュータの分類

疎結合型並列コンピュータにおいてプロセッサを結合する相互結合網は大きく間接網と直接網とに分けられる.間接網は,プログラム実行時あるいは動作中に接続を動的に変更できる結合網を言い,直接網は,接続形態がハードウェアの製作時点で固定的に決っている結合網を言う.間接網は必然的にプロセッサ間にスイッチ群を設置し,これらを制御することによって結合経路を構成する形態となる.スイッチの接続形態により,クロスバ網,Beneš網,オメガ網,バンヤン網等がある.いずれの網でも,スイッチは比較的単純な構成をしているが,ピン数の制約から LSI 化しにくいという問題がある.このため,間接網では結合網部のハードウェア構成が大掛かりとなってしまい,コスト高を招く.

直接網は、間接網よりも単純で、各プロセッサの通信用ポートを配線により固定的に接続したものである、結合のトポロジとしては以下のようなものがある.

#### 完全網

すべてのプロセッサが互いに接続された網である.プロセッサ数を N とするとプロセッサあたりのポート数は N-1 必要で,全結線数は N(N-1)/2 となる.このように多数のポートと結線が必要となるため,大規模システムの実現は困難である.

#### スター網

中心となる通信制御部に対しプロセッサが放射状に接続されたトポロジである.プロセッサあたりのポート数は1であり最も少ない.ただし,中心に位置する制御部のポート数はNであり,ここがボトルネックとなる.また,プロセッサ間の距離は,どのプロセッサをとっても2である.バスを通信制御部ととらえるとバス結合型もスター網の特殊な場合と言える.ただし,バスはプロセッサ間のデータ交換に対して能動的な役割を果たさないので,プロセッサ間距離は1と考えられる.

通信制御部は多数のプロセッサからのデータ転送要求が集中するため,それらが衝突しないように調停を行う必要がある.プライオリティ・エンコー

ダなどで構成されたアービタによる調停やポーリングにより制御部が調停機能を提供する集中制御方式は、バックプレーンなどを利用した同一筐体内のバスに利用される.集中制御方式では、プロセッサ番号の識別のために多数の制御線が必要となるが、バックプレーン利用のバスでは一般にデータ線やアドレス線も多数並列しているため、多少の制御線は問題とならない.CSMA/CD(Carrier Sense Multiple Access/Collision Detect)に代表されるような、プロセッサが自律的に調停を行うのが分散制御方式である.これは制御信号をデータ信号と同一の線上に載せることができるため、1本の同軸ケーブルや1組のより対線をバスとして利用してシリアル伝送する結合形態に適している.

#### 鎖網とリング網

隣接するプロセッサ同士を結合した網が鎖網である.両端のプロセッサ同士も接続すればリング網となる.プロセッサあたりのポート数は2であり,プロセッサ間距離の平均はN/4である.

#### 格子網 (ラティス,メッシュ,トーラス)

プロセッサを格子の交点に配置し,辺を通信路としたものが格子網である.格子網には正方格子,三角格子,六角格子等が考えられるが,正方格子 (メッシュ) が最も良く用いられる.正方格子の場合,プロセッサは4つのポートを持ち隣接する4つのプロセッサと通信できる.最左端と最右端,最上端と最下端同士を結ぶとトーラス網となる.プロセッサ間距離の平均は $\sqrt{N}/2$ である.

メッシュ網,トーラス網により結合された並列コンピュータは2次元アレイ型とも呼ばれる.2次元アレイ型並列コンピュータは,プロセッサのポート数が実現容易な範囲にあり,様々なアルゴリズムの並列化に適しているので,この結合網によるシステムが多数開発されている.

#### 木状網(ツリー)

ツリーのノードにプロセッサを配置し,枝を通信路とした網である.2進木の場合,プロセッサあたりのポート数は3,プロセッサ間の平均距離は $2\log_2 N$ である.根に近いプロセッサほど処理が重くなるため,葉ノードのプロセッサのみが演算処理を行い,他のノードはデータの中継のみを行う方式もある.

単純な木状網はLSIチップ内に効率よく埋め込むことができ、網の拡張も容易である.しかし、通信の迂回路がないため、ノードがひとつでも故障するとシステム全体が機能不全に陥るという問題がある.

#### 超立方体網 (2 進 n-キューブ, ハイパーキューブ)

$N=2^n$  個のプロセッサがそれぞれ n の通信ポートを持ち,プロセッサ番号を 2 進数で表した時にハミング距離が 1 のプロセッサ同士が結合している網が超立方体網である.プロセッサ間の平均距離は  $\frac{1}{2}\log_2 N$  である.二つの 2 進 n-キューブがある時に,各プロセッサに通信ポートを一つ増設し,同一番号のプロセッサ同士を結合することにより,容易に 2 進 n+1-キューブを構成することができる.このような数学的な美しさと,リング網,トーラス網,ツリー網などを包含していることから,汎用並列処理向きの相互結合網として注目されている.ただし,接続ポート数が他の結合網に比べて多いため,プロセッサのコストは高くなる傾向にある.

#### 1.3.2 本研究が対象とする並列コンピュータ

本論文では,実用的な領域で高コストパフォーマンスが得られるような人工知能システムの並列化をねらっている.この目的のために,まず,プロセッサあたりの通信ポート数が最も小さく低廉で容易に構成できるバス結合型を対象とする.バス結合型並列コンピュータは,VMEやPCI等の汎用バスに汎用のプロセッサボードを実装しただけも構成可能である.更に近年では,パーソナルコンピュータをローカルエリアネットワーク用のネットワークインタフェースによって接続した形態のBeowulf型並列コンピュータも多く製作されており,多くの人が容易にこのタイプの並列コンピュータを利用することが可能となって来ている.更に,汎用のマイクロプロセッサやその周辺部品を用いているため,これらの部品の進歩にも容易に追随でき,常に最新の部品性能を享受できる.このようなアーキテクチャにおいて,良好な性能が得られる並列化方式を考案できれば,その意義は大きいと考える.

更に、用途によっては絶対性能の追求も必要であるため、それぞれの応用システムに最も適すると考えられる結合網も対象とし、これらに対する並列化方式も検討する. PS に対しては、すでに多くの形態の結合網について研究されていることと、本論文で提案しているバス結合でも十分に良好な性能が得られることから、

他の結合網は取り上げない,BPに対しては,その演算に最適な結合網としてトーラス網を用いる.概念の類似判別では,概念の表現である意味ネットを直接マッピングするのに適したトポロジの網を対象とする.

# 第2章 プロダクションシステム条件 照合の並列化

ルールベースシステムは,人間の認知行動過程に基づいたシステムであり,エキスパートシステム(ES:expert system) はその代表的応用である.また,近年では,複数の能動的なシステムが知識を交換しながら協調して問題解決を行うマルチエージェント・システムへの応用も期待されている.

ルールベースシステムの推論機構としても最も一般的に用いられているプロダクションシステム (PS:production system)[72] は,条件照合・競合解消・実行の3フェーズからなる認知-実行サイクルにより推論を行う.この認知-実行サイクルの中で,条件照合フェーズは,ES を構成する多数のルール条件部と多数のワーキングメモリエレメントとの照合を行うため,その処理量が推論全体の中で大きな比率を占める.特に大規模なESでは,条件照合フェーズでの処理に消費される時間が非常に大きなものとなり,推論時間の大幅な増大を招くことになる.条件照合フェーズを高速に処理するために,RETE マッチ [17] や TREAT[65] といった条件照合処理の特性を利用して処理量を削減するアルゴリズムが開発されているが,それらをもってしても認知-実行サイクルの95%以上を条件照合フェーズが占めており[23],更なる高速化が必要とされている.

本章では、PSの推論を高速化するために、条件照合フェーズに最も多く用いられる RETE マッチ・アルゴリズムを並列処理する手法について論ずる.まず、PS と、その PS を成功に導く要因になったともいえる条件照合アルゴリズム RETE マッチについて説明する.次に、RETE マッチ・アルゴリズムで用いられている RETE ネットワークのモデル化を行い、そのモデルに基づいて並列度及び並列化時の速度向上度を計算する、RETE マッチ・アルゴリズム並列化の解析的評価法を提案する.続いて、RETE マッチ・アルゴリズムの並列化軸を抽出し、単純にこの並列化軸に沿った基本的な並列化方式を示す.これら基本並列化方式及び既存の並列化方式を,前述の解析的評価法に基づいて評価する.評価結果から、RETE

マッチ・アルゴリズムは本質的には数十倍の高速化の可能性があることがわかる.しかし,従来方式では,十分に並列性を利用できていないか,または,通信オーバヘッドの影響を受けやすいものであるため,現実的な通信バンド幅に制限した場合には10倍程度の速度しか得られないことを示す.

上記の並列化軸の抽出と評価により得た知見に基づき,RETE マッチ・アルゴリズムの並列性を引出し,実現容易な構成の並列コンピュータにおいても 10 数倍以上の速度向上度を実現できる TWIN(top two-input node distribution) 方式を提案する.TWIN 方式は,RETE ネットワークの構造的な並列性と,RETE ネットワークを構成するノードでの処理におけるデータ的な並列性を,通信の必要性が少なくなるように組合わせた方式である.このため,RETE マッチ・アルゴリズムが内包する並列性を十分に引出すと同時に,通信頻度も小さく抑えることが可能となり,実現が容易なバス結合型並列コンピュータでも 10 数倍から数十倍の速度向上比が期待できる方式である.従来方式を評価したと同一の解析的評価手法により TWIN 方式の性能を評価するとともに,実際の ES を用いて実験を行い,本方式の有用性を実証する.

# 2.1 プロダクションシステムと RETE マッチ・アルゴ リズム

本節では、PS の構成及び推論動作である認知―実行サイクルについて述べるとともに、認知―実行サイクル中で最も処理量が多い条件照合フェーズに用いられている、RETE マッチ・アルゴリズムについて説明する、

### 2.1.1 プロダクションシステム

1960 年代から 70 年代にかけて化学構造同定システム DENDRAL[16] や医学診断・治療支援システム MYCIN[85] など,専門家と同様に高度な判断ができる ESが開発された.70 年代後半になると,これら ES から知識表現技法及び推論制御技法を抽出し応用独立化を図った ES 構築用ツール[63] が開発されるに至る.これらに採用された代表的な推論制御技法が IF—THEN—型のルールに基づいて推論を行う PS である.PS を用いた ES 構築用ツールは,推論の高速化を実現する RETE マッチ・アルゴリズムを採用した OPS5[9] が開発されるに至り,ほぼ実用の域に

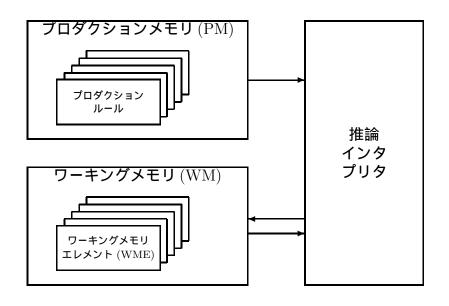

図 2.1: プロダクションシステムの構成

達した.その後,この OPS5 と同様の推論制御技法と RETE マッチ・アルゴリズムを採用した ES 構築ツールが多く開発されている [45].

PSは,ルールを格納するプロダクションメモリ (PM:production memory) と,事実データや中間データを格納するワーキングメモリ (WM:working memory),そして,PM,WMの双方を参照し解釈実行する推論インタプリタから構成される [72]. 図 2.1 に PS の構成を示す.PM には if—then—型のルールが格納される.個々のルールは,条件部または LHS(left-hand side) と呼ばれる条件要素の連接と,アクション部または RHS(right-hand side) と呼ばれる動作の集合とから構成される.WMには,事実,状況,推論の途中結果などの宣言的なデータが格納される.これらの個々のデータはワーキングメモリエレメント (WME:working memory element)と呼ばれる.PM は長期記憶 (long-term memory),WM は短期記憶 (short-term memory) と呼ばれることもある.

WME 及びプロダクションルールは具体的には以下のように記述される (OPS5[9] での文法を例としている).

#### WME

WME は , その WME が属するクラス名と , 0 個以上の属性名–属性値の組によって記述される . クラスはその WME が含む属性を定義しており , 以下のように書く .

これは Person というクラスが属性 name, father, mother, age, そして city-of-residence を持つことを表す.また, Move というクラスは, 属性 name, from そして to を持つことを表している.

WME は , 必ず上述のクラスのいずれかに属し , 以下のように記述される .

(Person ^name Teresa ^mother Helen ^father Cleve ^age 21 ^city-of-residence Swannanoa)

リストの先頭, すなわち上の例では Person, がその WME の属するクラスを表している. 以後の要素は,属性名とそれに対応する値の組の羅列である. この例では属性 name の値が Teresa であり,属性 mother の値が Helen,属性 father の値が Cleve,属性 age の値が 21,そして属性 city-of-residence の値が Swannanoa であることを表している.

実際は、WME には上述のクラスと属性名-属性値に加えタイムタグ (time tag) が付与されて WM に格納される.タイムタグは、WME を一意に識別するための番号で生成順にふられる.

#### プロダクションルール

プロダクションルールの例を以下に示す.

-->

(modify 1 ^city-of-residence <city2>)

(remove 2))

プロダクションルールであることを表す p に続き,ルール名 new-residence が記述される.次に条件部が記述され,-->以降にアクション部が書かれる.条件部は,複数の条件要素の連接として構成される.この例では,

(Person ^name <name1> ^city-of-residence <city1>)

及び

がそれぞれ条件要素である.

(Person ^name Teresa ^mother Helen ^father Cleve ^age 21 ^city-of-residence Swannanoa)

(Move ^name Teresa

```

^type permanent

^from-city Swannanoa

^to-city Pittsburgh)

```

がある場合に,第1,第2の両方の条件要素に含まれるパターン変数<name>,<city1>を,それぞれ Teresa,Swannanoa に束縛することが可能なため,この二つの WME はマッチする.また,同時に,第2の条件要素に含まれる変数 city2 は Pittsburgh に束縛される.

アクション部には,条件部を満足するWMEの組(インスタンシエーション)があった場合に実行されるアクションを記述する.アクションには,WMEに対する生成(make),更新(modify),削除(remove)といった操作や,情報の表示,システムの制御,他のプログラムの呼出しなどが記述される.WME操作のアクションにおいては,操作対象のWMEをそれがマッチする条件要素の番号で指定することができる(makeの場合は新たなWMEを生成するので当然ながら操作対象の指定はない).例では,modifyの対象は第1の条件要素にマッチしたWMEであり,removeの対象は第2の条件要素にマッチしたWMEである.ただし,ここでは説明を簡潔とするためこの記述法を用いているが,実際のプログラミングでは保守性を高めるためにパターン変数と同様の変数記述を用いて以下のように書くことが多い.

#### 2.1.2 認知-実行サイクル

ES構築ツールのほとんどで用いられている,やり直しなしの前向き PS(irrevocable forward chaining production system) では,次の3つのフェーズからなる認知—実行サイクル (recognize-act cycle) を繰り返すことによって推論を行う.

#### 1. 条件照合 (match)

すべてのルールについて,条件部とその時点の WM との照合を行う.条件部にマッチする WME の組が見つかった場合には,これらマッチした WME の組とルールそれ自体に関する情報 (これをインスタンシエーションと呼ぶ)を競合集合 (conflict set) に追加する.

#### 2. 競合解消 (conflict resolution)

条件照合が完了した時点で複数のインスタンシエーションが競合集合にある場合に,定められた戦略に従って実行すべきインスタンシエーションを一つだけ選び出す.この戦略を競合解消戦略(conflict resolution strategy)と呼ぶ. 代表的な競合解消戦略である LEX と MEA について以下に述べる.

#### LEX

LEX 戦略は,より新しい WME を含み,より厳しい条件を満足するインスタンシエーションを選択する戦略である.以下の手順で選択する

- 1. 以前選択したインスタンシエーションは選択しない(同一処理を永久に繰り返すことがないようにするため)

- 2. タイムタグが最も新しい WME を含むインスタンシエーションを 選択する.

- 3. 条件要素数の多いルールのインスタンシエーションを選択する.条件要素数が同じ場合には,条件部で行われるテスト数が多いインスタンシエーションを選択する.

- 4. 上記を順に適用してもインスタンシエーションを一つだけに絞り込めない場合は,残ったインスタンシエーションから任意に選択する.

#### MEA

MEA 戦略は LEX 戦略を拡張したもので,以下の手順でインスタンシエーションを選択する.

- 1. 以前選択したインスタンシエーションは選択しない(同一処理を永久に繰り返すことがないようにするため)

- 2. インスタンシエーションを構成する最初の WME(条件部の最初の 条件要素にマッチする WME) のタイムタグが最も新しいものを選 択する.

- 3. タイムタグが最も新しい WME を含むインスタンシエーションを 選択する.

- 4. 条件要素数の多いルールのインスタンシエーションを選択する.条件要素数が同じ場合には,条件部で行われるテスト数が多いインスタンシエーションを選択する.

- 5. 上記を順に適用してもインスタンシエーションを一つだけに絞り込めない場合は,残ったインスタンシエーションから任意に選択する.

MEA 戦略では,インスタンシエーションを構成する最初の WME のタイムタグを選択の基準とする条件が追加されている.これにより,第1条件要素に副目標や制御の切替えを記述して,推論動作の見通しを良くすることができる.

#### 3. 実行 (act)

競合解消によって選びだされたインスタンシエーションに対して,そのルールのアクション部を実行する.これをルールの発火(fire)と呼ぶ.一般に,アクション部にはWMEの追加・更新・削除といった操作が書かれるため,この実行フェーズによりWMの内容が変化する.

実行フェーズでの WME の追加・更新・削除によって, WM が変化し条件照合フェーズにおいて前回とは異る WME とルールの組合せがマッチすることになる.これにより競合解消フェーズにおいて新たなインスタンシエーションが選択され,このインスタンシエーションのルールが実行フェーズで発火し, WM の新たな変化を引起す.このような動作の繰返しにより推論が進んで行くことになる.この認知—実行サイクルが停止するのは次のような場合である.

- ◆ 条件照合フェーズが完了した時点で競合集合にインスタンシエーションが一つもない場合

- アクション部に明示的な停止命令が記述されたルールが発火した場合

これら停止条件が満足されると,推論インタプリタは停止し,推論完了となる.

### 2.1.3 RETE マッチ・アルゴリズム

条件照合フェーズでは,最も原始的には,PM に含まれる個々のルールに対し,PM に含まれるPM に含まれるPM に含まれるPM に含まれるPM に含まれるPM に含まれるPM に含まれるPM に含まれるPM に含まれるPM になった。PM に含まれるPM になった。PM に含まれるPM になった。PM に含まれるPM に含まれるPM になった。PM に含まれる個々のルールに対し、PM に含まれる個々のルールに対し、PM に含まれる個々のルールに対し、PM に含まれる個々のルールに対し、PM に含まれる個々のルールに対し,PM に含まれる個々のルールの条件部にマッチするかを調べることになる。PM に含まれる個々のルールの条件部にマッチするかを調べることになる。PM に含まれる個々のルールの条件部にマッチするかを調べることになる。PM に含まれる個々のルールに対し、PM に含まれる個々のルールに対し、PM に含まれる個々のルールに対し、PM に含まれる個々のルールに対し、PM に含まれる個々のルールに対し、PM に含まれる個々のルールに対し、PM に含まれる例の条件要素を持ついることになる。PM に対しない。PM に含まれる例の条件要素を持ついることになる。PM に対しない。PM に含まれる例の条件を表する。PM に含まれる例の条件を表する。PM に含まれる例の条件を表する。PM に含まれる例の条件を表する。PM に含まれる例の系件を表する。PM に含まれる例の条件を表する。PM に含まれる例の系件を表する。PM に含まれる例の条件を表する。PM に含まれる例の系件を表する。PM に含まれる。PM に含まれる。PM に含まれる。PM に含まれる。PM になる。PM になる。

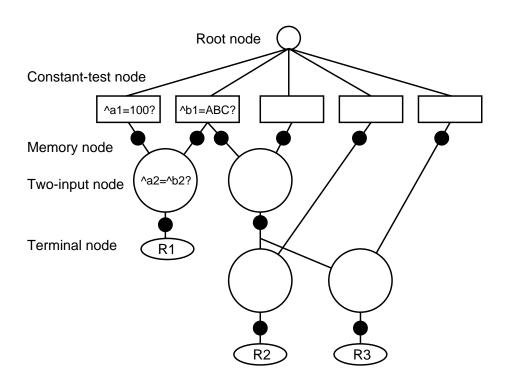

条件照合フェーズを効率化する方法は多く研究されており,そのなかで最も広く用いられているのが OPS5 を成功に導いた RETE マッチ・アルゴリズム [17] である.RETE マッチ・アルゴリズムは,前サイクルでの条件照合結果を記憶することによって,WME の変化分に対してのみ照合処理を行うことで毎回の条件照合フェーズでの照合処理を削減する.RETE マッチ・アルゴリズムでは,すべてのルールの条件部は RETE ネットワークと呼ばれる一種のデータフローグラフに展開され,変化した WME (トークンと呼ばれる) がこれを流れる事により照合が行われる.以下のようなルールに対する RETE ネットワークの概念図を図 2.2 に示す.

```

(p R1

(C1 ^a1 100 ^a2 <x>)

(C2 ^b1 ABC ^b2 <x>)

-->

(make C3 ^c1 <x> ^c3 ABC))

```

RETE ネットワークは次のようなノードから構成されている.

#### ルートノード (root node)

RETE ネットワーク全体の根となるノード. すべてのトークンはここから RETE ネットワークに注入される.

図 2.2: RETE ネットワークの概念図

#### 定数テストノード (constant-test node)

クラスが適合しているか,属性の値が与えられた定数値と等しいかといった条件要素内に閉じたテスト (条件内テストと呼ぶ) を行うノード . 1 入力ノード (one-input node) とも呼ばれる .

#### 2 入力ノード (two-input node)

複数の条件要素に書かれた同名のパターン変数が同一の束縛値を持つかどうかをテスト (条件間テストと呼ぶ) するノード.

#### 終端ノード (terminal node)

ルールの条件部に記述されたすべての条件要素にマッチしたトークンが到達するノード.終端ノードに到達したトークンはルールの情報とともにインスタンシエーションとして競合集合に追加される.

#### メモリノード (memory node)

定数テストノード及び 2 入力ノードを通過したトークンを記憶するノード. 定数テストノード直下のメモリノードを  $\alpha$  メモリ,2 入力ノード直下のもの を  $\beta$  メモリと呼ぶ. ルートノードから定数テストノードまでは条件要素内に閉じたテストを行うネットワークであり判別ネットまたは弁別ネットと呼ばれる.また,2入力ノードで構成されるネットワークは条件要素間のテストを行うもので結合ネットと呼ばれる. RETE マッチ・アルゴリズムでの条件照合処理は以下のような手順で行われる.

- 1. 実行フェーズでの WM 更新によって WME が変化すると , その変化分がトークンとして RETE ネットワークに注入される .

- 2. ルートノードから伝播したトークンは,定数テストノードにおいて条件要素内の定数値との比較が行われる.このノードでの比較が成功すると,その下つながる枝に伝播する.

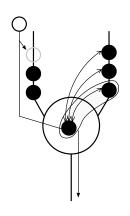

- 3. 定数テストノードを通過したトークンは,そのノードと接続された2入力ノードへ伝播するとともに,その枝上のメモリノード(αメモリ)に記憶される.トークンが伝播してきた2入力ノードは活性化(activation)される.2入力ノードでは,条件要素にまたがる変数の照合を行うために,入力となる2本の枝のメモリノードに記憶されたすべてのトークンとの突合せが行われる.この処理は結合演算(join)とも呼ばれる.ここでの比較が成功すると,それらマッチした二つのトークンの組を新たなトークンとして,その下の枝へと伝播させる(図2.3).

- 4. 更に従属に 2 入力ノードが接続されている場合には,伝播してきたトークンはその 2 入力ノードに入力されるとともに,枝上のメモリノード(β メモリ)に記憶される.2 入力ノードでは上のステップと同様の突合せが行われる.従属につながった 2 入力ノードがある限り,同様の処理が繰返される.

- 5.2入力ノードをすべて通過して終端ノードに到達した場合,そのトークンは照合に成功したことになる.ルールの情報とともにインスタンシエーションとして競合集合に登録される.

上記の動作をする RETE マッチ・アルゴリズムが条件照合フェーズを効率的に 処理できるのは,以下の二つの特徴による.

#### 中間結果の保存

RETE ネットワークの  $\alpha$  メモリ, $\beta$  メモリには,以前のサイクルでの条件照合の途中結果が保存されることになる.このため,サイクルごとにすべての WME に対して条件テストを繰り返す必要がなくなる.すなわち,各サイクルでの条件照合はルールの発火によって変化した WME に対してのみ行えば

図 2.3: 2 入力 ノードでの処理

良いことになる.実際の応用システムの測定によれば,サイクルごとに条件 照合が必要となるのは RETE ネットワークのごく一部に過ぎない [23].また, ES の規模が増大しても,サイクルごとに活性化される 2 入力ノード数は,それほど大きくならない.このことが,RETE マッチ・アルゴリズムを用いることにより大規模 ES でも条件照合を実用的な時間で処理できる大きな要因となっている.

#### ネットワークの共有

RETE ネットワークでは , 異なるルール間でも , 同一の照合条件のものは一つのノードとして共有する . このノードの共有により定数テストノードの数は  $1/4 \sim 1/9$  に , 2 入力ノードの数が  $2 \sim 3$  割削減され , 実行速度が 1.4 倍向上すると報告されている [23] .

上述の通り,中間結果の保存による再計算の大幅な削減と,ネットワークの構造による同一条件照合の共有により,RETEマッチ・アルゴリズムは大幅な速度向上を実現している.しかしながら,これを用いてさえも,条件照合フェーズが推論時間のうち90%以上を占める報告されている[23].

## 2.2 プロダクションシステム高速化手法

RETE マッチ・アルゴリズムは多くの ES 構築ツールで採用されているが,これを用いてさえも条件照合フェーズが推論の 90%以上もの処理時間を占めている.計画問題向けで認知—実行サイクルを多く繰り返すタイプの ES や,探索型でルー

ル発火により多数の WME が変化する ES では,条件照合フェーズの処理時間が原因で推論に非常に長い時間を要することになる.このため,条件照合フェーズを更に高速化し,推論時間をより短縮することが望まれている.

RETE マッチ・アルゴリズムの高速化法としては,RETE ネットワークの構造 や個々のノードでの処理を最適化して処理量を減らす方法 [5, 43] と,複数のプロセッサで分割処理する並列化による方法 [21, 75] とがある.本論文では並列化による方法に焦点をあてており以降の節で詳述するので,本節では RETE ネットワークの最適化について概観する.

RETE マッチ・アルゴリズムを用いた推論インタプリタでは, $\alpha$  メモリ, $\beta$  メモリを単純なリストとして実装しているものが多い.この場合には,条件間テストが 2 重ループで計算され,処理時間はトークン数の自乗に比例する.これを高速化するために, $\alpha$  メモリ, $\beta$  メモリへのトークンの記憶を単純なリストとせずハッシュ表で実現する方法が提案されている [24].ハッシュ表による実装を行うと,条件間テストの多い ES に対しては 2.5 倍~3.5 倍程度の性能向上が得られると報告されている.

更に高度な手法として,RETE ネットワークをより効率的な構造に変形することが考えられている.ART[12] や YES/OPS[82] 等では,条件間テストの実行順序や 2 入力ノードの結合構造を ES 設計者が指定する方式を提案している.効率の良い構造を指定するためのヒューリスティックスとして次のようなものが知られている.

- ▶ トークン数の少ない条件要素から条件テストを実行する

- 変更量の少ない条件要素から条件テストを実行する

- RETE ネットワークの結合構造を共有する

しかしながら、ES 設計者にとって、これら3種類のヒューリスティックの相互作用を考慮しながら最適なRETE ネットワーク構造となるようなルールを記述することは容易ではない.この問題を解決するために、ES の動作特性に基づいてRETE ネットワークの構造を自動的に最適化する手法が提案されている [43].この手法は、RETE ネットワークのコストモデルを構築し、ES の実行を測定して得られたパラメータに基づいてコストが最小となるように RETE ネットワークの結合を最適化する.これにより ES 設計者の試行錯誤によることなく、また、保守性

を損なわずに最適化が行われることになる.更に,人手の試行錯誤による最適化によりも良い性能が得られると報告されている.

## 2.3 条件照合処理の並列性と従来の並列化方式

本節では、RETE マッチ・アルゴリズムの処理の並列性について論じ、従来提案されている方式がどのような並列性をどの程度の粒度で利用しているか、すなわち従来方式の並列化軸における位置付けを示す.

RETE ネットワークはデータフローグラフととらえることができる.トークンがこのグラフを流れるデータであり,グラフの各ノードでは条件内テストや条件間テストなど,トークンあるいはトークンの組に対する比較演算が行われる.特に2入力ノードでは,それぞれの入力枝上のメモリノードに記憶されたトークンをペアとして比較が行われるため,比較演算を多数回繰り返すことになる.したがって,複数のトークンが同時に伝播する経路としての構造的な並列性,ノードにおいて多数のテストが同時に行われるノード処理の並列性の二つの軸が考えられる.以下では,この二つの並列性について詳述する.

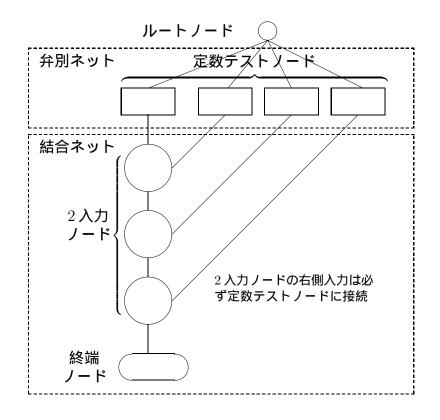

#### RETE ネットワーク構造の並列性

RETE ネットワークには,1個のルートノードがあり,ここがトークンの入口となる.ルートノードには,定数テストノードから構成される弁別ネットへの枝が接続されている.弁別ネットでは,すべてのルールのすべての条件要素に対する定数テストノードが含まれるため,ルートノードから弁別ネットへの枝はPMに含まれる全条件要素に相当する数だけに分岐していることになる.

弁別ネットの下段には2入力ノードと終端ノードから構成される結合ネットが接続されている.RETE ネットワークの2入力ノードは,二つの入力のうち一方は必ず弁別ネット内の定数テストノードに接続される.したがって,結合ネット最上段に位置する2入力ノードは二つの入力がともに弁別ネットに接続され,それ以下の段では,例えば左側の入力は1段上の2入力ノード,右側の入力は弁別ネットに接続されることになる(図2.4).RETEマッチ・アルゴリズムの特徴であるルール間でのノード共有のために,一つの定数テストノードが複数の2入力ノードへ接続されている場合がある.同様に,ある2入力ノードの下段には一つ以上の2入力ノードが接続される場合がある.

図 2.4: 2 入力 ノードの連鎖

ルートノードからトークンが入力された後は,RETE ネットワークをデータフローグラフとしてトークンが流れることになる.このため,弁別ネットでは,ルートノードから分岐した枝の数だけ並列に処理が可能である.結合ネットでは,従属に接続されている2入力ノードの連鎖は逐次に処理される必要があるが,ある連鎖と別の連鎖は並列に処理できる.なお,2入力ノードは二つの入力を持つため,両入力からのデータ到着を待つ同期処理が必要なように見えるが,次に述べるように,RETE マッチ・アルゴリズムの場合にはそのような同期は不要である.2入力ノードでは,一方の入力よりトークンが入来し,そのトークンと他方の入力上のメモリノードに記憶されたトークンとの比較が行われる.すなわち,トークンが入来した際の比較相手となるトークンは既にメモリノードに記憶されているものだけである.したがって,トークンが入来し次第処理を開始することができ,同期は不要なのである.

以上のように,RETE ネットワークの構造に着目した場合,弁別ネットでは定数テストノードごとに,結合ネットでは2入力ノードの連鎖ごとに並列処理が可能である.ただし,このような並列処理可能な単位に基づいて単純に処理を分割

しプロセッサにマッピングしても、良い結果が得られるとは限らない.RETE ネットワークを分割するとノード間をつなぐ枝が切断される.この場合には、分割した処理の単位の間で通信が必要となり、通信オーバヘッドが生じるため、枝を多く切断するほど処理速度が低下する.また、一つのトークンのみに注目すれば2入力ノードの連鎖は逐次にしか処理できないが、認知—実行サイクルで複数トークンが発生したり上段の2入力ノードでの照合によって複数のトークンが発生する場合があり、この場合には従属に接続されたノードはパイプライン的に並列処理できる.したがって、このような場合には、2入力ノードの連鎖も分割した方が、より多くの並列性を利用できる.

#### ノードでの処理の並列性

弁別ネットの各ノードでは,一つのトークンに対して,単純な比較が行われるだけである.このため,個々の定数テストノードでの処理には並列性はない.もっとも,その処理の単純さゆえ,弁別ネットでの処理時間がRETEマッチ・アルゴリズム全体の処理時間に占める割合は小さい.

弁別ネットを通過したトークンは、結合ネットの2入力ノードのどちらか一方の入力に伝播して来る.そして,もう一方の入力の直上にあるメモリノードに記憶されたすべてのトークンとの条件間テストが行われる.ここで,テストに成功するものがあれば,成功したトークンのペアの情報を持つ新たなトークンが生成され,より下段の2入力ノードへと伝播させられる.テストに成功するトークンがある限りペア情報を持つ新たなトークンの生成と伝播が続けられ,トークンが終端ノードに達するとインスタンシエーションとして競合集合に追加される.

上述のように,2入力ノードではメモリノードに記憶されたトークンの数だけテストが繰り返されるため,これを並列に処理することが可能である.並列化に際しては,入来したトークンは,その2入力ノードを処理すべきすべてのプロセッサに複写される必要がある.一方,メモリノードに記憶されたトークンはどれかのプロセッサ上にあれば良く,また,テストも他のプロセッサからは独立に処理することができる.2入力ノード処理の並列化では,テスト対象となるトークンは異なるものの,テストする内容は同一であるため,処理量のばらつきは小さいと考えられる.また,プロセッサ間の通信量は,メモリノードに記憶されるべきトークンのプロセッサへの蓄積方法及び配布方法に依存する.

#### 従来の並列化方式

上記の考察から,それぞれの並列性を利用したいくつかの方式を容易に考えることができるし,実際にそれらの多くは既に提案されている.以下に,そのような並列化方式を列挙する(図 2.5).

#### ルール並列化方式

個々のルールを並列処理の単位とする自明な方式である.RETE ネットワークの構造的並列性の着目した方式の一種と位置付けることができるが,ネットワークの分割と同時に,複数ルールで共有されていたノードがそれぞれの処理単位に複写されることになる.これは,並列化に伴う処理量の増加,すなわち分割損をもたらす.

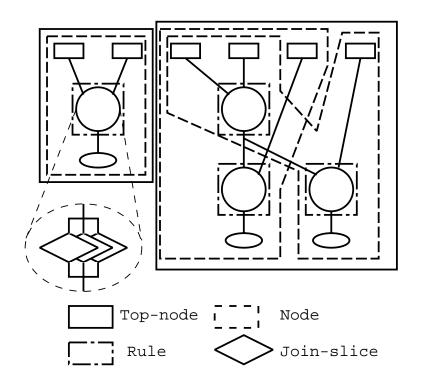

#### トップノード並列化方式

結合ネット最上段の2入力ノード(トップノードと呼ぶことにする)とそれに接続されたすべてのノードを並列処理の単位とする方式である[100].トップノードに基づいてRETEネットワークを分割することにより,結合ネットでは枝を切断することがなく,通信の必要がない.一方で,粒度はルール並列化方式よりも更に大きくなる.また,分割した結合ネットの複数に共有されている定数テストノードは,複写してそれぞれの処理単位に含ませる.これによって,ルール並列化方式同様に分割損が生ずる.ただし,弁別ネットの処理量は結合ネットでの処理量にくらべて圧倒的に小さいため,この分割損による処理時間の増加は小さいと予測される.

#### ノード並列化方式

個々のノードを処理単位とする方式である [26] . 上記考察で述べたように,1 個のトークンだけの動作に着目すると,従属に接続された2 入力ノードは逐次的に処理しなければならず,ノードにまで処理を分割する利点はほとんどないが,RETE ネットワーク内を複数のトークンが流れる場合には,このような2 入力ノードの連鎖でもパイプラインとしての並列処理が可能である.ノードの入力と出力の枝がすべて切断されるため,トークンの伝播があるごとにプロセッサ間通信が必要となる.

#### ジョインスライス並列化方式

2 入力ノードにおけるトークンのテストのそれぞれを処理単位とする方式で

図 2.5: RETE マッチ・アルゴリズムの並列化方式

ある[53].ノード処理における並列性を最大限に利用する方式で,メモリノードに記憶された個々のトークンに対して1個ずつのプロセッサを割り付ける.トークンが伝播して来た場合には,これが複写されて各プロセッサに入力される.各プロセッサは,入来したトークンと自分が持つトークンとのペアに対するテストを1回だけ行い,成功すればトークンのペアの情報を含む新たなトークンを生成して下段のノードが割り付けられたプロセッサに流す.構造的にはノード並列化方式と同様に入力と出力の枝がすべて切断されており,トークンの伝播がプロセッサ間通信の機会となるが,枝そのものが照合対象となるトークンの数だけ分岐することになるため,通信量は更に多くなる.

## 2.4 RETE ネットワークのモデル化による並列化方式 の評価

前節で列挙した RETE マッチ・アルゴリズム並列化方式のなかには,既に提案されその性能が報告されている方式も多い.しかし従来の報告での評価手法は,特定の ES を対象としたシミュレーション評価によっており,報告ごとにサンプル

ES が異なるため,並列化方式相互の比較が困難であった.RETE マッチ・アルゴリズムの並列化による速度向上度は,対象となる ES の問題特性に大きく依存するため,並列化方式を相互に比較するためにはこの問題特性を一致させる必要がある.また,問題への依存性も比較するために,広範囲の ES 特性にわたる評価が望まれる.

本節では、RETE マッチ・アルゴリズム並列化方式の速度向上度を解析的に評価する手法を提案する。本評価法では、RETE ネットワークをモデル化し、このモデルに基づいて並列度や処理量を ES の問題特性で表現する。これを用い、与えられた ES 問題特性に対する速度向上度を計算する推定式を導出する。この推定式を用いて並列化方式の比較を行い、各方式の適用領域、ハードウェアの要求条件を明確化する。

## 2.4.1 エキスパートシステムの問題特性

ここでは、並列化方式の速度向上度に影響を与える ES 問題特性を抽出する.並列化方式は RETE ネットワークの構造とノードでのデータ処理に基づいて処理を分割しているため、これらに影響するパラメータが必要である.ただし、パラメータから構造や処理内容が完全に特定できる必要はなく、速度向上度の推定が可能となるような統計的な数値が得られれば十分である.

このような観点から ES 問題特性として表 2.1 及び表 2.2 に示すパラメータを抽出した.表 2.1 は RETE ネットワーク構造の推定に必要なパラメータ,表 2.2 は ノードでの処理特性の推定に必要なパラメータである.

#### 構造を支配する問題特性パラメータ

個々の条件要素に対し定数テストノードが生成されるため,ルール数とルールあたりの条件要素数の平均値がわかれば弁別ネットでのノード数が推定できる.また,個々のルールに対し従属接続される2入力ノードの数は,条件要素数に依存する.異なるルールに同一の条件テストがある場合,それに対応するノードは共有される.したがって,ルール数Rと1ルールあたりの条件要素数E,そして,同一条件内テストの比率 $S_c$ がわかれば,ノード数や接続枝数などのRETEネットワークの構造に関する値を推定できる.

#### 動作を支配する問題特性パラメータ

ルールあたりのアクション数 A は , 一つのルールに含まれる  $\mathrm{WME}$  操作アク

表 2.1: RETE ネットワークの構造を支配する問題特性パラメータ

| パラメータ        | 記号    |

|--------------|-------|

| ルール数         | R     |

| ルールあたりの条件要素数 | E     |

| 同一定数テストの比率   | $S_c$ |

ションの数の平均値である.また,アクション部更新動作比率  $\beta_m$  は,WME 操作アクション中の WME 更新動作の割合である.WME の生成操作及び削除操作はそれぞれトークンを 1 個しか生成しないが,WME 更新操作では,トークンが 2 個 (旧い内容の WME の削除と新たな内容の WME の生成) 発生するため,1 認知—実行サイクルあたりのトークン発生数を推定するために  $\beta_m$  は必要である.クラス数 L は ES に含まれるクラスの種類である.また,WME の数は,生成,削除動作により推論中に変化するが,ここではその平均値を用いる.これらは,ES ソースプログラムの分析,ES 設計段階での見積によって得られる.

条件内テストの成功確率  $\alpha_c$  及び条件間テストの成功確率  $\alpha_j$  は,個々のノードで異なるはずであるが,ここでは RETE ネットワークの全体的な動作特性が推定できれば十分なため,一定値と仮定する. $\alpha_c$ , $\alpha_j$  は ES の設計に大きく依存し,正確な値を得るには実際に ES を動作させ測定する必要があるが,設計時に見当がつく認知—実行サイクルごとの照合成功ルール数から概算する事もできる.一般には,条件内テストを緩くし条件間テストで最終的に絞り込むので, $\alpha_c$  は 10 ~ 数十%, $\alpha_i$  は 1%以下といわれている [23].

以上のパラメータから,RETE ネットワーク内で活性化されるノード数,活性化されたノードにおける条件テスト回数などを推定することができる.

## 2.4.2 RETE ネットワークのモデル化

RETE ネットワークを構造的にも動作的にも特徴づけているのは 2 入力ノードである . 2 入力ノードは , 定数テストノードを通過したトークンとメモリノードに蓄積されたすべてのトークンとの条件間テストを行うため , 処理量が他ノードに比べ非常に大きい . 更に , あらゆる種類のノードは必ず 2 入力ノードに接続され

表 2.2: RETE ネットワークの動作を支配する問題特性パラメータ

| パラメータ         | 記号           |

|---------------|--------------|

| ルールあたりのアクション数 | A            |

| 実行部の更新動作比率    | $\beta_m$    |

| WME <b>数</b>  | W            |

| クラス数          | L            |

| 条件内テストの成功確率   | $\alpha_c$   |

| 条件間テストの成功確率   | $\alpha_{j}$ |

るため,このノードの特性が推定できれば他ノードの特性も付随的に求まる.そこで,ここでは2入力ノードのふるまいに着目し,RETE ネットワークのモデルを構築する.

代表的な ES についての分析 [23] に基づけば,以下の事実が導き出される.

#### 事実

- 2入力ノードの出力枝の分岐数は比較的少数

- ルールあたりの条件要素数の度数分布は条件要素数の増大に伴い指数 関数的に減少

この事実より,2入力ノードを以下のようモデル化する.

#### 2入力ノードのモデル

- 出力枝の一定の分岐率 B を持つ

- 一つのノードは確率 P で終端する

このモデルによれば,図 2.6 のように,出力が平均 B 本あり,そのノードから出る枝の 1 本が一定確率 P で終端ノードに接続されることになる.したがって,従属接続される 2 入力ノードは一段毎に (B-P) の割合で減少する.すなわち,2 入力ノードの従属段数 (条件要素数 - 1 に等しい) の度数分布は指数関数的に減少し,上記事実に良くあう.このモデルを規定するパラメータ B 及び P と問題特性との関係を以下に示す.

図 2.6: 2 入力 ノードのモデル

#### EとPの関係

1段目の2入力ノード数を $d_o$ としたときに,n段目で終端するノードの数 $d_n$ はこのモデルより $d_n=d_oP(B-P)^{n-1}$ となる.これより,全終端ノード数 $D_t$ は,

$$D_t = \sum_n d_n = \sum_n d_o P(B - P)^{n-1} = d_o \frac{P}{1 - (B - P)}$$

(2.1)

となり、その ES における従属段数の平均値 e は、

$$e = \sum_{n} n \frac{d_n}{D_t} = \sum_{n} n \frac{d_o P(B-P)^{n-1}}{d_o \frac{P}{1-(B-P)}} = \frac{1}{1-(B-P)}$$

(2.2)

で計算できる.ところで,E=e+1であるから,

$$P = (B-1) + \frac{1}{E-1}. (2.3)$$

ルールあたりの条件要素数の平均 E は ES のプログラムを見れば容易に得られるから,残る分岐数 B が決まれば RETE ネットワークの特性は一義的に決定できる. B は ES のルール記述を分析すれば正確に求まるが,一般には,共通部分が少ないもので 1.1,共通部分が多いものでも 1.9 程度と報告されている [23] .

## 2.4.3 RETE ネットワークの諸特性

ここでは,並列化による速度向上推定のために必要となる RETE ネットワークの 構造的特性及び処理量特性を導出する.構造的な特性としては以下のものがある.

定数テストノードの総数  $D_1$ : 弁別ネットには定数テストノードが含まれるため, これが弁別ネットでのノード総数となる.

- 2入力ノードの総数  $D_2$ : 結合ネットは,2入力ノードと終端ノードから構成されている.終端ノードはルール数に等しいことは自明であるし,最下段の2入力ノードに付随するものと考えることができる.したがって,2入力ノードの数が結合ネットの構造を支配することになる.

- 定数テストノードから 2 入力ノードへの接続枝数 S: 弁別ネットと結合ネットとを接続する枝の数である. 粒度が大きく結合ネットの枝を切らない分割をするルール並列化方式やトップノード並列化方式でも,弁別ネットと結合ネットと結ぶ枝は切断される. したがって,通信オーバヘッドを推定するために,この枝数の推定が必要となる.

また,処理量特性としては以下のものがある.これらは,並列化のためにRETE ネットワークを分割した際のそれぞれの処理単位の処理量を支配する.処理量ばらつきが大きいと,プロセッサ間で負荷の不均衡が生じて速度向上を阻害するし,分割損によって総処理量が増加しても速度が低下する.したがって,並列化による速度向上を推定するために,これら特性が必要となる.

- 活性化される定数テストノード数  $O_1$ : 認知—実行サイクルの実行フェーズにおいて発生したトークンは,条件照合フェーズにおいて RETE ネットワークのルートノード入力される.ルートノードからは弁別ネットへトークンが流れ込み,そのトークンが持つクラスと同一のクラスの条件内テストを行う定数テストノードが活性化される. $O_1$  は,1 個のトークンによって活性化される定数テストノードの延べ数を表す.

- 弁別ネットを通過するトークン数  $T_t$ : 活性化された定数テストノードにおいて条件内テストが行われ,テストに成功したトークンが結合ネットへと流される.  $T_t$  は,この定数テストノードでテストに成功するトークンの数を示す.

- 活性化される 2 入力ノード数  $O_2$ : 定数テストノードを通過したトークンは , それが接続された 2 入力ノードを活性化する . また , 2 入力ノードでテストに成功すると , 新たなトークンが生成され , 更に下段の 2 入力ノードを活性化する .  $O_2$  は , 1 個のトークンの入力によって活性化される 2 入力ノードの延べ数を表す .

- 2 入力ノードでの平均テスト回数 *j*: 2 入力ノードでは,入力されたトークンと,対 向する入力上のメモリノードに記憶されたトークンそれぞれとをペアとして

条件間テストを行う.したがって,2 入力ノードでは,条件間テストをメモリノードに記憶されたトークンの数だけ繰り返すことになる.j は,この条件間テストの回数を示す.

認知—実行サイクルあたりの発生トークン数 M: 上記の特性値は,1 個のトークンによって活性化されるノード数やテストの回数であった.1 回の認知—実行サイクルでは,複数のトークンが発生する場合が多い.1 個の WME に対して更新が行われるとトークンが 2 個発生(旧い内容の WME 削除と新たな内容の WME 生成を行ったと等価のため)するし,ルールのアクション部には任意数のアクションを記述できるため,1 回のルール発火でいくつもの WME が生成・更新・削除される場合もある.M は,1 回のルール発火あたりのトークンの発生個数を表す.

これまで述べてきた ES 問題特性と 2 入力 ノードのモデルとを用いて , これらの RETE ネットワーク特性を導出する . ただし , 速度向上の計算には , 処理量の平均 , 分散など統計量がわかれば十分なため , 導出に際し以下のような近似を行った .

#### 近似

- 各クラスに対する条件要素の数は均一とする.また,トークンもこれに 対し均等に発生することとする.

- 各ノードの照合成功率は一定とする.

RETE ネットワーク特性は以下のように導出される.

#### 定数テストノードの総数 $D_1$

ルール間で共通の定数テストがなければ,条件要素の総数に等しいので $R \cdot E$ である。実際には $S_c$ だけ共通化されるので,

$$D_1 = R \cdot E(1 - Sc) \tag{2.4}$$

となる.

#### 2入力ノードの総数 $D_2$

まず,m段目の2入力ノードのノード数を $D_{2(m)}$ とすると,この2入力ノー

ドのうち終端ノードに接続されている数  $b_m$  は,ノード終端の確率が P であることから,

$$b_m = D_{2(m)}P \tag{2.5}$$

となる.これを全段にわたって総和した数はルール数Rに等しいから,

$$R = \sum b_m = P \sum D_{2(m)} = PD_2 \tag{2.6}$$

となる.2入力ノードの総数 $D_2$ に対して解いて,

$$D_2 = R/P \tag{2.7}$$

を得る.また,

$$D_{2(m)} = D_2\{1 - (B - P)\}(B - P)^{m-1}$$

(2.8)

である.

#### 定数テストノードから2入力ノードへの接続枝数 S

RETE ネットワークでは 2 入力ノードの右側入力は必ず定数テストノードに接続されている . また 1 段目では左側入力も定数テストノードに接続される . したがって

$$S = D_{2(1)} + \sum D_{2(m)} \tag{2.9}$$

となり, $D_{2(1)}$ を $D_2$ で表わして代入すれば,

$$S = D_2\{2 - (B - P)\} \tag{2.10}$$

を得る.

#### 活性化される定数テストノード数 01

1個のトークンによって活性化される定数テストノードは,入力されたトークンと等しいクラスをテストするノードの数に等しい.したがって,全定数テストノードをクラス数で除した値,

$$O_1 = D_1/L (2.11)$$

となる.

弁別ネットを通過するトークン数 T<sub>+</sub>

活性化した定数テストノードでのテストは  $\alpha_c$  の確率で成功するので,テストに成功する定数定数テストノード数は  $O_1\cdot\alpha_c$  となる.定数テストノードは平均  $S/D_1$  の分岐を持ち,これらすべてにトークンが配布されるから,弁別ネットを通過し結合ネットへと入力されるトークン数は,

$$T_t = O_1 \cdot \alpha_c \frac{S}{D_1} = \frac{S \cdot \alpha_c}{L} \tag{2.12}$$

となる.

活性化される2入力ノード数 $O_2$

弁別ネットからトークンが結合ネットへと伝播することにより  $T_t$  個の 2 入力 ノードがまず活性化される.個々の 2 入力ノードには,従属に平均 E-1 段の 2 入力ノードが接続されている.下段のノードは必ずしも活性化されると は限らないが,ここでは,平均的には全段が活性化されるとして,

$$O_2 = T_t(E - 1) (2.13)$$

とする.

#### 平均照合回数 i

2 入力ノードでの照合回数は,そのノードの入力上のメモリノードに記憶されたトークン数に等しい.これは推論を通して変化するが,弁別ネットを通過したトークンは必ずメモリノードに記憶されるため,全推論過程での平均を考えれば,全発生トークンのクラスあたりの数(クラスあたりのWME数に等しくなる)と条件内テスト成功率との積,

$$j = \frac{W}{L}\alpha_c \tag{2.14}$$

になる.

認知-実行サイクルあたりに発生するトークン数 *M*

トークンは生成及び削除操作で1個,更新操作で2個発生するため,平均実行要素数と1実行要素あたりのトークン発生数との積,

$$M = A(1 + \beta_m) \tag{2.15}$$

となる.

表 2.3: RETE ネットワークの構造的特性

| 項目                     | 記号    | 計算式                  |

|------------------------|-------|----------------------|

| 定数テストノードの総数            | $D_1$ | $R \cdot E(1 - S_c)$ |

| 2入力ノードの総数              | $D_2$ | R/P                  |

| 定数テストノードから2入力ノードへの接続枝数 | S     | $D_2\{2-(B-P)\}$     |

表 2.4: RETE ネットワークの処理量特性

| 項目                 | 記号    | 計算式                  |

|--------------------|-------|----------------------|

| 活性化される定数テストノード数    | $O_1$ | $D_1/L$              |

| 弁別ネットを通過するトークン数    | $T_t$ | $S \cdot \alpha_c/L$ |

| 活性化される2入力ノード数      | $O_2$ | $T_t(E-1)$           |

| 2入力ノードでの平均照合回数     | j     | $(W/L)\alpha_c$      |

| 1 認知サイクルで発生するトークン数 | M     | $A(1+\beta_m)$       |

以上の結果を表 2.3 及び表 2.4 にまとめる.これらの値を用いることにより,平均活性化ノード数や各ノードでの平均テスト回数,認知サイクルでの総テスト回数などが計算できる.例えば,1 認知-実行サイクルあたりの結合ネットでの総テスト回数は, $O_2 \cdot j \cdot M$  と計算できる.

## 2.4.4 速度向上度の推定式

ここでは、上記の RETE ネットワークのモデルに基づいて、ES 特性と並列化方式を代入するだけで速度向上度を推定できる一般式を導出する.

認知-実行サイクルを逐次処理した場合の処理時間を  $T_0$  とすると,並列化時の同サイクルの処理時間 T は,

$$T = \frac{QT_0}{N}\gamma + T_C \tag{2.16}$$

で表される、ここで、それぞれの記号は

N: プロセッサ数

Q: 処理の分割による総処理量の増加係数

γ: 負荷ばらつきによる処理時間の増加係数

T<sub>C</sub>: 通信オーバヘッドによる処理時間の増加

を表す.ところで,RETE マッチ・アルゴリズムの処理は,ノードでの照合とその結果であるトークンの伝播であるため,トークン伝播に伴うデータ転送量は各プロセッサで処理するトークン数とノード数とに比例すると考えられる.したがって,通信オーバヘッドによる処理時間の増加 $T_C$ は,プロセッサあたりの処理量に比例し,

$$T_C = \frac{QT_0}{N}C_o \tag{2.17}$$

と書ける. $C_o$  は並列化方式に固有の通信オーバヘッド係数である.したがって処理時間は,

$$T = \frac{QT_0}{N}\gamma + \frac{QT_0}{N}C_o = \frac{QT_0(\gamma + C_o)}{N}$$

(2.18)

となり,速度向上度Uは,

$$U = \frac{T_0}{T} = T_0 \frac{N}{Q \cdot T_0(\gamma + C_o)} = \frac{N}{Q(\gamma + C_o)}$$

(2.19)

となる.処理量増加係数 Q は,RETE ネットワークをどのように分割したかにより容易に決定できる.例えばルール並列化方式の場合,オリジナルの RETE ネットワークでは,定数テストノードと 2 入力ノードとの接続枝は S 本であるが,定数テストノードを共有しないことにより  $R\cdot E$  本に増加する.定数テストノード数も 2 入力ノード数もともにこの枝数に比例して増加し,処理量も同様に増加するから,この場合は,Q=RE/S となる.

また,通信オーバヘッド係数  $C_o$  は,認知—実行サイクルあたりの総テスト回数に対する通信回数の割合を  $C_R$ ,一対のトークンのテスト時間に対する 1 トークン転送時間の比を  $C_C$  とすると,

$$C_o = C_R \cdot C_C \tag{2.20}$$

となる.

つぎに,負荷ばらつき係数  $\gamma$  について考える.通信オーバヘッドを除いた並列 処理時間  $T_P$  は最も処理時間のかかるプロセッサにより支配され,

$$T_P = \max(T_1, T_2, \cdots, T_N) \tag{2.21}$$

となる.ここで, $T_i$  は  $\mathrm{PE}_i$  の処理時間を表す.負荷ばらつき係数は,負荷均等と想定した処理時間と  $T_P$  との比と考えられるから,

$$\gamma = \frac{\max(T_1, T_2, \cdots, T_N)}{\sum T_i / N} \tag{2.22}$$

となる. $T_i$  について詳細化すれば,RETE ネットワークの諸特性を用いて  $\gamma$  を定式化できることがわかる.

いま,分割した個々の処理  $g_j$  の処理時間を  $t_j$  とする.これらの中には相互に逐次的に処理されなければならないものもあるから,そのような処理を集めて並列化の処理単位を構成する.それらの処理単位を  $G_1,G_2,\ldots,G_m$  と表す.また, $G_j$  の処理時間を  $T_{G_j}$  と書く事にする.処理単位をプロセッサに均等に割り付ければ,プロセッサあたりの処理単位の数は m/N 個となるから,あるプロセッサでの処理時間  $T_i$  は m/N 個の  $T_{G_j}$  を加算したものとなる.すなわち,

$$T_i = \sum_{j=x}^{j=x+m/N} T_{Gj},$$

(2.23)

ただし,x=(i-1)m/N+1 である.この定式化に基づき,以下の手順で  $\gamma$  が計算できることになる.

- 1) モデルにより  $T_{G_j}$  の分布を計算. 例えば,ルール並列化方式の場合,処理時間は処理単位に含まれる2 入力ノードの数に比例すると考えられるので,2 入力ノード従属段数と相似な分布(指数分布)となる.

- 2) 上で求めた分布を持つ母集団から m/N 個取り出した標本値の総和の分布 (すなわち  $T_i$  の分布) を求め,その平均値  $E(T_i)$  を計算 [52] .

- $T_i$  なる分布を持つ母集団から N 個の標本を取り出した場合の最大値の分布を求め,その平均値  $E\{\max(T_i)\}$  を計算.

- 4)  $\gamma = E\{\max(T_i)\}/E(T_i)$  を計算.

$T_{Gj}$  の分布を解析的に求めることができれば,以上の手順により $\gamma$  も解析的に計算できる.また,モデルから直接に分布が求まらなくとも,実際の ES を動作させて処理時間を測定し,既知の分布関数に近似してやることで,以後は解析的に計算することが可能である.

なお, $\gamma$ は定性的に以下の性質を持つ.

表 2.5: 並列化方式と好適なアーキテクチャ

| 並列化方式 | 処理単位       | アーキテクチャ            |

|-------|------------|--------------------|

| ルール   | 個々のルール     | 放送機能を持つ (トークンを全 PE |

|       |            | に配布するため) バス結合型     |

| トップ   | トップノードとそれに | 放送機能を持つ (トークンを全 PE |

| ノード   | 連なるすべてのノード | に配布するため) バス結合型     |

| ノード   | 個々のノード     | ツリー , メッシュなどのネットワー |

|       |            | ク結合型               |

| ジョイン  | ノード内での個々の  | トークン配布,収集機構を持つ階    |

| スライス  | トークン照合     | 層的ネットワーク結合型        |

- 処理単位の数が多ければ処理時間が平均化されるため,処理量の分布や逐時性に関わらず $\gamma$ は小さくなる.逆に,並列性が小さければ,処理量分布,逐次性が $\gamma$ に与える影響は顕著となる.

- 処理単位間の逐次性が大の場合には, $G_j$  が含む処理の数が多くなり,処理単位内での処理量ばらつきが平均化されるため, $\gamma$  は逐時性に支配される.

- 逐時性小の場合は処理単位の処理量分布が大きく影響する.

#### 2.4.5 各並列化方式の解評価析と考察

本節では,前述した並列化方式のそれぞれに対し,速度向上推定式の各項を計算し,速度向上度の比較を行う.各方式に対して,それぞれ好適と考えられる並列プロセッサのアーキテクチャを仮定し,そのアーキテクチャ上での速度向上度を評価する.並列化方式とアーキテクチャの対応を表2.5に示す.並列化方式とアーキテクチャから,速度向上推定式の各項は表2.6の様に求める事ができる.

ルール並列化方式とトップノード並列化方式の処理量は処理単位に含まれる2 入力ノード数に比例とすると考えられるため,処理量の分布は2入力ノード数の 分布と相似になる.これはまた,ルールあたりの条件要素数の分布と相似でもあ る.逐次的に処理されるものは処理単位内に閉じているため,処理単位間での逐 次性はない.また,通信はトークンがRETEネットワークに入力された際に,そ れを全プロセッサに配布するために必要となるだけである.放送機構をもったバ

表 2.6: 速度向上度推定式の項の値

|             | トップノード     | ルール             | ノード             | ジョインス                   |

|-------------|------------|-----------------|-----------------|-------------------------|

|             |            |                 |                 | ライス                     |

| 処理単位の数 $n$  | $T_t/L$    | $Q \cdot T_t/L$ | $T_t \cdot M/L$ | $T_t \cdot M \cdot j/L$ |

| 処理量増加係数 $Q$ | $\simeq 1$ | $R \cdot E/S$   | 1               | 1                       |

| 処理量分布       | 処理単位あ      | 処理単位あ           | ノード内で           | ほぼ均一                    |

|             | たりのノー      | たりのノー           | の比較回数           |                         |

|             | ド数の分布      | ド数の分布           | の分布に相           |                         |

|             | に相似        | に相似             | 似               |                         |

| 逐次性         | なし         | なし              | ノードの従           | 無視可                     |

|             |            |                 | 属数              |                         |

| 通信比率 $C_R$  | $\simeq 0$ | $\simeq 0$      | 1/j             | 2                       |

スによりプロセッサを結合してあれば,これは一度の放送だけで済むため,通信 オーバヘッドはほとんど無視できる.

ノード並列化方式では,処理量のばらつきはノード内での比較回数のばらつきとノードの接続関係による逐次性とに起因する.前段の2入力ノードの処理が完了しない限り次の段の2入力ノードの処理は開始できないため,ノードの逐次性の方がより深刻であり,処理量のばらつきもこれが支配的である.通信は個々のノードの処理ごとに1回必要となる.1ノードあたりj回のテストが行われるのであるから,総テスト回数に対する通信回数の比率は,1/jとなる.

ジョインスライス並列化方式は個々のテストが処理単位であるから処理量ばらつきはほとんどない.一方,テストを行うために他のプロセッサからトークンを受信し,テスト結果を他プロセッサに送信する必要があるため,総テスト回数の2倍の回数の通信が必要となる.

以上により速度向上度を推定するのに必要な項がすべて導出できるので,これを用いて各並列化方式を評価する.まず,適当なパラメータを持つ ES を想定し,それに対する条件照合フェーズの速度向上度を計算して,各並列化方式の実用性能とスケーラビリティを概略的に調べる.次に,ES パラメータを変化させ,問題特性に対する速度向上度の感度を評価する.

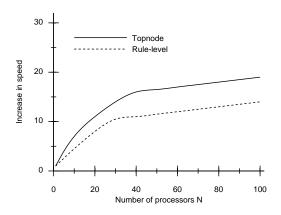

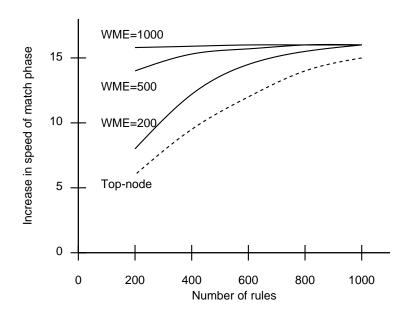

図 2.7 は ,表 2.7 に示すパラメータを持った中規模 ES に対して条件照合フェーズの速度向上度を計算した結果である . ノード並列化方式やジョインスライス並

表 2.7: 評価に用いた ES 特性

R:300 A:2.0  $\alpha_c:0.35$  E:3.5  $\beta_m:1.0$   $\alpha_j:0.07$  L:7 B:1.2 W:250  $S_C:0.3$

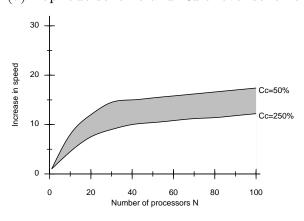

列化方式の細粒度方式に対しては , 1 個のトークンの転送時間 ( 1 トークン転送時間の 1 トークン照合時間に対する比  $C_c$  ) を変化させている . この値と表 2.6 に示した通信発生の割合  $C_R$  との積が , 通信オーバヘッド係数  $C_o$  となる .

条件照合フェーズの消費する時間が推論全体の約90%程度とすると,条件照合フェーズをいかに高速化しても,推論全体の速度向上度は10倍程度が限界となる.このことから,条件照合フェーズとしても,10倍~数十倍程度の速度向上が意味のある高速化であるといえる.この観点で図2.7をみると,トップノード並列化方式は辛うじて意味のある速度向上が達成できる事がわかる.また,ルール並列化方式は処理量増加が原因となりトップノード方式より常に速度向上が小さい.

より粒度の細かいノード並列化方式は分割した処理の数が多いため一見より大きな速度向上が得られるように思える。しかし実際には、従属接続されたノードの逐次性により並列処理できる処理単位が限定されてしまうため、グラフからわかるようにトップノード並列化方式などの粗粒度の方式と同程度の性能しか得られない。ただし、認知—実行サイクルごとに多数のトークンが発生するESでは、従属接続ノードをパイプライン処理できるので、より大きな速度向上が期待できる。また、この方式は相互結合網のデータ転送性能が低いと性能が低下する。

ジョインスライス並列化方式は,高速のデータ転送が可能ならば非常に大きな速度向上が期待できる.しかし,データ転送性能が低い場合には,トップノード方式よりも速度向上が小さい.一対のトークン比較は数マシンステップで済むため,この方式の性能を十分に引き出すには,トークンの転送も数マシンステップで行うことが可能な相互結合網が要求される.

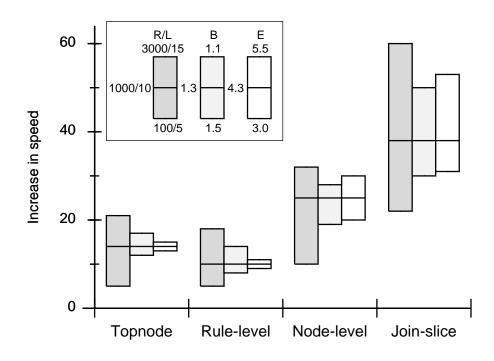

ES のパラメータを変化させた場合の速度向上度の変動範囲を図 2.8 に示す.変化させたパラメータは,RETE ネットワーク構造への影響が大きく,速度向上の規定要因となるものである.他のパラメータは,その変化が推論の絶対時間に影響するが,並列化による速度向上にはほとんど影響しないと考えられる.この図

(a) トップノード方式, ルール方式

(a) Topnode scheme and Rule-level scheme

(b) ノード方式

(b) Node-level scheme

(c) ジョインスライス方式

(c) Join-slice scheme

図 2.7: 解析評価による速度向上特性

図 2.8: 速度向上の問題依存性

から,並列化方式の速度向上はルール数 (すなわち ES 規模) に最も大きく影響される事がわかる.また,小規模領域ではトップノード方式やルール方式などの粗粒度方式は数倍の速度向上度しか得られないことがわかる.これは処理単位の数が不足してプロセッサの負荷ばらつきが増加するためである.すなわち,ルール数が十分に大きい領域 (おおよそ 1000 ルールを超えるような規模の領域) にしか,これら粗粒度方式は適用できない.ジョインスライス方式は,本質的には,あらゆる ES 特性領域で十分な速度向上が期待できるが,前述のように,プロセッサ間のデータ転送速度が遅い場合は,性能が急激に低下する.

以上から,ルール並列化方式やトップノード並列化方式などの粗粒度方式では,通信の発生頻度が低いため,バス結合型などの低廉にハードウェアを構成可能なアーキテクチャでも並列化方式の持つ本質的な速度向上を実現できることがわかる.しかし,その速度向上度の絶対値として,ルール数が1000以上と大きい場合には意味のある値となるが,そうでなければ満足な性能は期待できない.一方,ジョインスライス並列化方式のような細粒度方式では,どのようなES特性に対しても十分な速度向上が期待できるが,実際にこれを達成するためには,非常に高速な相互結合網が必要となることがわかる.このようなハードウェアは高価となる.

## 2.5 TWIN 方式の提案

前節の評価結果から,従来方式では,安価に構成できるハードウェアでは限定的な ES 特性の領域でしか十分な速度向上が得られないことがわかった.逆に,広範囲の ES 特性に対して十分な速度向上を得ようとすれば,高価なハードウェア構成となってしまうことがわかった.前述のとおり条件照合フェーズ並列化による速度向上度は,その目標を 10 倍~数十倍に置いている.この程度の速度向上を得るために,非常に高速な相互結合網を持つ高価なハードウェアを用いるのは得策ではないだろう.比較的安価に構成できるハードウェア構成で,この目標を広範囲の ES 特性に対して達成できる並列化方式が望まれる.本節では,このような並列化方式として TWIN 方式を提案する.

まず、RETE マッチ・アルゴリズムの中核を担っている2入力ノードについて、詳細に考察する.この考察に基づき、ジョインスライス並列化方式のように照合ごとに通信を要求することなく、2入力ノードを多数のプロセッサで処理できる方法を示す.そして、この方法を利用し、通信発生の割合を小さく抑えたまま構造的な並列性と2入力ノード処理の並列性の両方をひきだす、TWIN 方式について詳述する.

## 2.5.1 2 入力 ノードに関する考察

RETE ネットワーク及び各ノードでの処理は 2.1.3 でも説明したが , ここでは 2 入力ノードの構造及び処理についてより詳細に述べ考察する .

2 入力ノードは弁別ネットの下位に位置して結合ネットを構成し,ルールごとにいくつかの連鎖があり,最下段は終端ノードに接続されている.2 入力ノードでは,ルールの条件要素にまたがるテスト (条件間テスト) が行われる.より具体的には,ある条件要素の条件内テストを通過した WME と別の条件要素の条件内テストを通過した WME で同一のパターン変数が同一の値に束縛されているかをテストする.2 入力ノードでのテストを通過した場合,その WME ペアの情報をすべて含むトークンを生成して下段に位置する 2 入力ノードに伝播させる.したがって,この下段の 2 入力ノードでは 3 つの WME に含まれるパターン変数の一致をテストできることになる.このような連鎖構造により,ルールの条件要素が E 個あった場合に,これから二つ取った組合わせの数は E(E-1) もあるにもかかわらず,E-1 個の 2 入力ノードですべての条件間テストを行うこ

とができる.条件要素の中にはパターン変数を持たないものもあり,この場合は条件間テストは不要である.しかし,上記の連鎖構造を成立させるためには,このような条件要素に対しても2入力ノードが必要となる.2入力ノードは,パターン変数の一致をテストする以前に WME の組を生成する機能も担っているからである.このような条件要素に対しては,あらゆるトークンの組に対してテストが成功する2入力ノードが対応する.このため,パターン変数の多寡にかかわらず,2入力ノードの連鎖は,必ず E-1 個のノードを含む.

このような連鎖構造とするために,2 入力ノードの一方の入力 (例えば図 2.4 では右側の入力) は必ず WME1 個のみの情報が伝播して来る弁別ネットに接続されている.すなわち,最上段に位置する 2 入力ノード (これを特にトップノードと呼ぶ) は両入力とも弁別ネットに接続され,2 段目以降の 2 入力ノードは一方の入力が上段の 2 入力ノード,他方の入力が弁別ネットに接続されるという構造となっている.

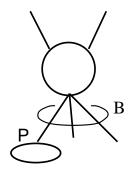

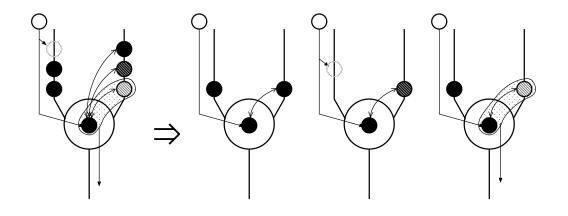

次に,図2.3を参照して,トークンが到来した場合の2入力ノードでの動作を詳述する.ここでは,図にあるように,左側入力からトークンが到来する場合について述べているが,左右を入れ換えれば右側入力から到来した場合でも同じとなる.

- 1. 左側の入力にトークンが到来する

- 2. トークンを左入力直上のメモリノードに記憶する

- 3. 右入力直上のメモリノードから記憶されたトークンを一つ取出す (ただし取出 したトークンをメモリノードから取除くわけではない)

- 4. 到来したトークンと取出したトークンとをペアとして, この 2 入力ノードに 割り付けられた条件間テストを行う

- 5. テストが成功すれば, そのペアの情報を含む新たなトークンを生成し出力に 流す

- 6. 右入力直上のメモリノードから記憶されたすべてのトークンを取出してテストするまで3~5を繰り返す.

このように,2入力ノードにおいて,到来したトークンとのペアを作ってテスト対象となるのは,メモリノードに記憶されたトークンである.したがって,2入力ノードでの処理量は,メモリノードに記憶されたトークンの数に支配されることになる.

ところで、メモリノードに記憶されたトークンというのは、最初からそこに記

憶されていたわけではない.上の2番目のステップにあるように,トークンが到来した際に記憶されたものである.すなわち,右側入力直上のメモリノードに記憶されているのは,いずれかの時点で右側の入力に到来したトークンなのである.上の動作からわかるように,メモリノードへの記憶と条件間テストとは,必ずしも不可分ではない.つまり,到来したトークンに対し,メモリノードへの記憶を行わずに,条件間テストを行うことも可能である.もちろん,逐次処理でこのようなことをすれば,本来メモリノードに記憶されなければならないトークン,すなわち条件にマッチしたWME,が照合の対象から洩れてしまうことになり,正しい結果が得られなくなってしまう.しかし,このことは,2入力ノードでの処理を並列化しようという場合には重要な示唆を与える.メモリノードに記憶されたトークンを複数のプロセッサに分散させることができれば2入力ノードを並列に処理することができる.そしてこのトークン記憶の分散は,メモリノードへの記憶を制御することにより実現できそうに見える.

#### 2.5.2 2入力ノード処理の並列化

上記考察から,メモリノードへの記憶動作を適切に制御すれば,2 入力ノードでの照合処理を複数のプロセッサに分散させることが可能になると予測できる.ここでは,2 入力ノード処理並列化のための具体的な記憶制御法及び処理手順を提案する.

一つの 2 入力ノードを N 個のプロセッサに分散させることを考える.処理をこれらに分散させ,かつ,重複したテストを行わないためには,どれかの一つのプロセッサのメモリノードだけにトークンを記憶すれば良い.また,プロセッサを通じて処理量ができるだけ均等となるためには,各プロセッサのメモリノードに記憶されたトークンの個数が均一となるようにすれば良い.このことから,次のようにして,2 入力ノードを並列化できる.

まず,2 入力ノードを N 個のプロセッサに割り付け,それぞれのプロセッサに  $0\sim N-1$  までの番号をふる.またトークンにも一連番号をふることにする.トークンは既にタイムタグとして一連番号を持つので,これを流用すれば新たな番号を付与するまでもない.2 入力ノードが割り付けられたすべてのプロセッサにトークンが入力されるようにする.各プロセッサは,トークンが到来した際に,この2 入力ノード及び直上のメモリノードの処理として以下のようにする.

- トークンの番号を N で除した余りがプロセッサの持つ番号と同一ならば , そのプロセッサはメモリノードへの記憶を行う .

- トークンに対するテストはすべてのプロセッサで行う。

本並列化手法による2入力ノードを動作を図2.9に示す.白丸が到来したトークンである.逐次処理の場合(図の左端)は、到来したトークンが左側のメモリノードに記憶されるとともに、1台のプロセッサで右側のメモリノードに記憶された3個のトークンのすべてとのテストが行われる.ここでは、メモリノードの一番下にあるトークンがテストに成功し、新たなトークンが生成されて下段に伝播させられる.並列化した場合には、図の右側に示したように、まず到来したトークンはこの例では中央のプロセッサのメモリノードに記憶される.次に各プロセッサは、自己が持つメモリノードの内容を対象としてテストを行う.右側のメモリノードには、過去の処理によって、3個のトークンはそれぞれ異なったプロセッサに記憶されているため、それぞれ1個のトークンに対してテストが行われる、結果として、逐次処理の場合と同じく、3個のトークンに対するテストすべてが行われることになる.ここでは、右端のプロセッサでテストが成功し、このプロセッサにおいて新たなトークンが生成され下段に伝播させられる.

図には示されていないが,更に右側入力よりトークンが到来した場合を考えてみよう.上と同様に,到来したトークンはまずどれか1個のプロセッサの右側メモリノードに記憶される.続いて,各プロセッサでそれぞれが持つ左側メモリノードの内容に基づいたテストが行われる.右端及び左端のプロセッサでは過去のいつかの時点で記憶されたトークンを対象とし,中央のプロセッサでは先ほど到来して記憶されたトークンを対象としてテストを行う.この場合も結果として逐次処理と同じ3個のトークンに対するテストが行われることになる.

このように、複数のプロセッサに 2 入力ノードを割り付け、メモリノードへの記憶をどれか 1 個のプロセッサが行うことにより、テストを繰り返す過程で処理対象となるトークンの記憶が分散され、条件照合処理を並列化することができる、また、このようにしても、逐次処理と全く同じくすべてのトークンに対してテストが行われ、洩れが生ずることはない、

図 2.9: 2入力ノード処理の並列化

#### 2.5.3 2入力ノードの連鎖の並列化

前節で述べたのは、単独の2入力ノードの並列化の方法であった.実際のRETE ネットワークは2入力ノードの連鎖構造を持っているため、更に、下段につながる2入力ノードでの処理も考慮する必要がある.特に問題となるのは、テストが成功した場合に、新たに生成したトークンを下段に伝播させることができるのは、そのテストを担当したプロセッサのみであるということである.上述の並列動作では、2入力ノードが割り付けられたすべてのプロセッサに到来トークンが入力されることが前提となっている.下段の2入力ノードでも同様の動作をさせるためには、テストに成功した場合に生成されたトークンは全プロセッサに転送される必要がある.このような転送は、ジョインスライス並列化方式と同様に、通信オーバヘッドを大きくする原因となる.

このオーバヘッドを避けるために,2入力ノードーつひとつを処理単位とするのではなく,その連鎖を処理単位とし以下のような動作とする.

- 2入力ノードの連鎖を処理単位として複数のプロセッサに割り付ける

- 最上段の2入力ノード(トップノード)に対しては前述の並列処理を行う

- 2段目以降の2入力ノードに対しては,逐次処理と同様にすべてのプロセッサがメモリノードへの記憶もトークンのテストも行う

このような処理方式で,2段目以降の2入力ノードでも処理が並列化され,かつ, テストが洩れなく行われることを示そう. まず、上段とその下の段の2入力ノードとの間にあるメモリノードがどのようにトークンが記憶されているか考える.上段では並列にテストが行われ、テストに成功したプロセッサではトークンが生成されて下段に伝播させられる.そのプロセッサにおいて伝播してきたトークンは、すべてそのプロセッサのメモリノードに記憶される.ところで、上段の2入力ノードにおけるテストの成功は必ずしも1個とは限らず、全く成功しない場合もあれば多数成功する場合もある.特に、パターン変数を持たない条件要素に対応する2入力ノードでは、テストが必ず成功するのでメモリノードに記憶されたトークンすべてに対し成功することになる.多くのトークンを処理する間には、これらのテストの成功はどのプロセッサにも均等に起こると考えられる.したがって、従属接続された2入力ノード間のメモリノードには、均等にトークンが記憶されると考えられる.また、言うまでもなく、すべてのプロセッサのメモリノード内容の和集合は、逐次処理でのメモリノードの内容と同一となる.このようにメモリノードに記憶されたトークンがプロセッサ間で分散しているため、2段目以降の2入力ノードに対して弁別ネットからトークンが到来した場合にも、その2入力ノードは並列に処理されることになる.

一方,上段でテストに成功して生成されたトークンそのものの処理に関しては,それが生成されたプロセッサでしか処理できない.しかし,上述のように,多数のテストが成功するような場合は,複数のプロセッサがそれぞれに自プロセッサで生成したトークンを処理するため,並列化されることになる.また,対向する入力上のメモリノードには到来したすべてのトークンを記憶しているため,照合対象となるトークンの洩れはない.

弁別ネットからのトークンは,2入力ノードの連鎖が割り付けられたすべてのプロセッサに転送される必要があるが,これは粗粒度方式と同様である.連鎖の中で発生したトークンは,そのプロセッサ内で処理されるため,通信の必要はない.このように本方式は,粗粒度方式と同程度の通信頻度で,2入力ノードでの処理の多くを並列化できるものである.

#### 2.5.4 TWIN 方式

上記で,2入力ノードの連鎖のみについて,少ない通信頻度で並列化する方法を構築した.これに基づいた RETE マッチ・アルゴリズム並列化方式である TWIN 方式を提案する.

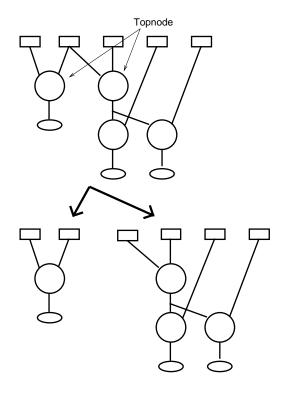

図 2.10: TWIN 方式の構造並列化

TWIN 方式 [100] は、本質的に通信不要な構造的粗粒度並列化をベースとして、上述の通信を増加させないデータ並列性を組み合わせ、良好な負荷バランスを実現する方式である.TWIN 方式の構造並列化は、トップノード並列化方式と同一である.図2.10 に示すように、第1段目の2入力ノード(トップノード)とそれに続く2入力ノード,及びそれらの2入力ノードに接続されたすべての定数テストノードからなる部分的なネットを一つの並列処理の単位とする.この並列処理単位として分割されたネットをRETEサブネットと呼ぶことにする.2入力ノードはトップノードから従属に接続され、かつ右側の枝は必ず定数テストノードに接続されているため、以上のような分割により切断される枝はルートノードに接続する枝のみとなる.ルートノードからの枝に流れるのは同一のトークンであるため、トークン入力時に一斉にトークンを配布すれば、その後の照合処理では通信は一切不要である.なお、この構造並列化では、定数テストノードが複数のRETEサブネットに複写される場合があり、これにより総処理量が増加する.しかし、定数テストノードでの処理量は2入力ノードでのそれに比較して非常に小さいので、大きな問題とはならない.

この RETE サブネットは,2入力ノードの連鎖を完全に含んでいるので,前節

で提案した並列化を施すことによって,2入力ノード処理も並列化される.2入力 ノード並列化の並列度は,原理的にはメモリノードに蓄積されたトークン数まで 可能であるが,実際には蓄積トークン数に応じてRETE サブネットを動的に複写 するのは困難なので推論開始前に固定的に与える.

このようにTWIN 方式では,粗粒度の構造並列化に,通信頻度を増加させないように2入力ノード処理の並列化を組合わせることにより,粗粒度方式と同一の通信頻度で,より大きな並列度を得ることを可能としている.したがって,バス結合型などの比較的安価に構成可能なアーキテクチャで,広い範囲のES特性に対して十分な速度向上が得られることが期待できる.

## 2.6 TWIN 方式の解析的評価

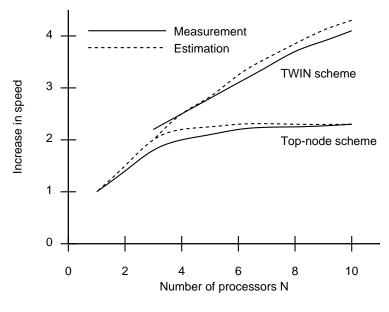

2.4節で提案した速度向上度の推定式により TWIN 方式を評価する . ES パラメータは従来方式の評価に用いたと同一のものを用い , プロセッサ数は 16 , 2 入力 ノード処理の並列度は 3 とした . 結果を図 2.11 に示す .

結果のグラフからわかるように,2入力ノード並列化の効果により,常にトップノード並列化方式より大きな速度向上度を得ている.また,トップノード並列化方式の速度低下が顕著なルール数が少ない領域で,特により大きな性能改善が得られている.特に,WME数が十分にあれば,小ルール数でも満足な速度向上が得られることがわかる.

## 2.7 実験による評価

TWIN 方式の性能評価をより確かとするため、小規模な実験システムを用いた評価を行い、解析結果との比較を行う、両評価の結果が一致すれば、実験ではカバーできない領域でも解析による結果がほぼ正しいと考えることができる。

実験システムはマイクロプロセッサボードを汎用バスで結合したものである (図 2.12) . バスはトークンを全 PE に配布するための放送機能を持っている . また , プロセッサ数は最大 10 である .

実験用として 2 地点間の最短経路を深さ優先法により探索する小規模 ES を構築して用いた.本 ES はルール数 23, WME 数 1000 で構成される,実験によって得られた条件照合フェーズの速度向上を図 2.13 に示す.実線が実測値,破線が推定

図 2.11: TWIN 方式の解析評価結果

Communication Bus (with broadcast mode)

図 2.12: 実験システムの構成

値である.解析評価の場合と同様にデータ並列度は3とした.また,トップノード並列化方式の結果もあわせて示している.結果のグラフからわかるように,トップノード並列化方式では2倍程度で速度向上が飽和している.これは,ES 規模が20ルール程度であり,RETE ネットワークの構造的分割だけでは負荷ばらつきが大きいことを示している.一方,TWIN 方式では,2入力ノード処理並列化の効果により10PEでも速度向上が飽和せずに上昇している.しかし,ルール数が極端に小さいため,速度向上比率(速度向上/PE数)は低めである.100ルール規模のES を用いれば,より高い速度向上比率が得られ,16PEで10倍程度の速度向上が得られると予測される.

また,図からわかるように,推定結果は実測とは良く合っており,誤差は10%

図 2.13: 実測結果

程度である.推定式は,並列化方式の適用領域の比較や,その方式に適したアーキテクチャの探索に利用するには十分な精度を持っていることが示された.

## 2.8 まとめ

本章では, PS の条件照合フェーズの並列化について論じた.

まず,並列化方式の速度向上を解析的に評価する手法を提案し,これに基づき, 従来から提案されている代表的な並列化方式を評価した.解析的評価手法では,2 入力ノードのふるまいに着目して RETE ネットワークをモデル化し,ネットワークの構造や処理量を ES パラメータにより表現する.これに基づき,負荷ばらつき, 通信オーバヘッドなどを考慮して,速度向上推定の一般式を導出し,評価用 ES や シミュレータを用いる事なく様々な並列化方式の評価を可能とした.

本解析評価手法を用い,代表的な並列化方式について,ESパラメータを広範囲に変化させて比較評価を行った,その結果,従来の方式では,小ルール数の領域で負荷ばらつきにより十分な速度向上が得られないか,または,非常に高速なトークン転送を行うための特殊なハードウェアが必要とされることを明らかにした.

次に,通信オーバヘッドと負荷ばらつきが共に少ない TWIN 方式を提案した.

本方式は、RETE ネットワークを構造的に粗く分割することによりノード間での通信を不要とし、2 入力ノードでの条件間テスト処理を並列化することにより小ルール時の負荷ばらつきを抑えている。解析手法と実際の ES を用いた実験により評価を行い、小ルール数の領域でも十分な速度向上が得られることを確認した。

# 第3章 プロダクションシステム向け 並列コンピュータ Presto

PS条件照合フェーズの並列化方式として2章においてTWIN方式を提案した.本章では,この方式に基づき推論インタプリタを高速実行するべく開発した並列コンピュータ "Presto" について述べる.

PSの推論処理のうち90%以上を条件照合フェーズが占めるため,このフェーズの並列化が最も重要なことに間違いはない.しかし,条件照合フェーズが十分に高速化されると,他のフェーズでの処理が速度を支配する要因となって来る.したがって,推論インタプリタの動作を高速化するためには,条件照合フェーズのみならず,他のフェーズも可能な限り並列処理する必要がある.また,現実の並列コンピュータではプロセッサは有限であり,その個数は実行開始前に固定的に決っている.一般に,並列処理のために分割した処理単位はプロセッサ数よりも多いため,複数の処理単位を一つのプロセッサに割り付けることになる.プロセッサ間の負荷ばらつきはこの割り付けの方法に依存し,これが性能に影響を与える.特に,本論文が対象としている疎結合型アーキテクチャにおいては,実行中に処理単位をプロセッサ間で異動することは,通信オーバヘッドによる性能の著しい低下を引き起こすため,事実上不可能である.したがって,実行以前に負荷ばらつきを推定し,これが小さくなるように処理単位をプロセッサへ割り付ける手法が必要となる.

本章では、まず、条件照合フェーズ以外の並列化及び処理単位の割り付けを含む、認知-実行サイクルの総合的な並列化方式を提案する.つぎに、この並列化方式に好適なアーキテクチャについて論じ、そのアーキテクチャに基づいて実際に開発した並列コンピュータのハードウェアについて説明する.更に、推論インタプリタをこのハードウェアに実装する際の課題を明らかにし、その解決法を提案する.最後に、開発したシステムを実際のESを使って評価する.

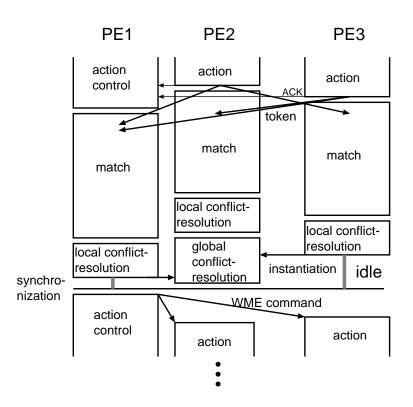

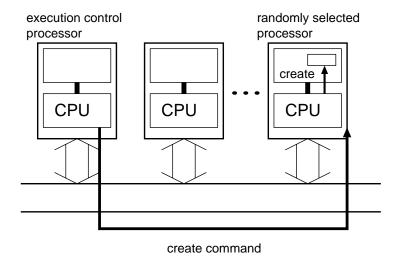

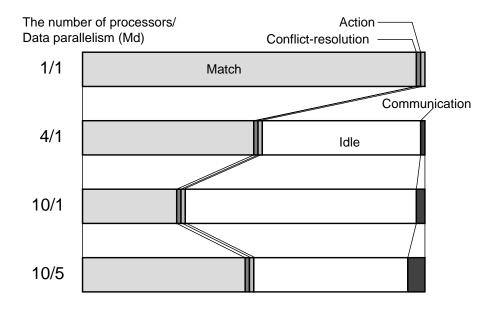

図 3.1: 並列化認知サイクル

## 3.1 認知-実行サイクルの並列化方式

TWIN 方式の通信不要性を活かし、全体として高速な並列推論インタプリタを実現するためには、競合解消フェーズ・実行フェーズでも通信を抑え、かつ、バランス良く並列化する必要がある.ここでは、条件照合フェーズにおける TWIN 方式と同様に通信頻度が小さいことを特徴とする、認知―実行サイクル全体の並列化方式を提案する.また、本方式は、通品頻度のみならず、認知―実行サイクルのフェーズ移行の際に必要となる同期を少なく抑えることも特徴としている.

本方式における認知—実行サイクル全体の動作を図 3.1 に示す . 図に示すように , 各プロセッサが非同期に条件照合・競合解消を行い , 全体の競合解消 (グローバル競合解消) 終了時に一回だけ同期がとられる . その後のルール実行も (アクション要素は複数あれば) 並列に処理され , 実行を終了したプロセッサから順次照合フェーズへ移行する . このように , 認知—実行サイクル中に同期は 1 回のみであり , また , プロセッサ間の通信も図に示すように , トークン発生時 , グローバル競合解消時 , そしてルール実行時に必要となるのみである .

以下では,順を追ってより詳細に本並列化方式の動作を述べる.

実行フェーズで発生したトークンは,放送によってすべてのプロセッサに入力される.条件照合フェーズはTWIN方式により並列に処理される.TWIN方式は,RETEネットワークをRETEサブネットに分割してプロセッサに割り付けているため,各プロセッサの競合集合には,割り付けられたRETEサブネットに対応するインスタンシエーションが蓄積される.

条件照合フェーズが終了すると競合解消フェーズに移行するが、本方式では、そのプロセッサが持つ競合集合内でのローカルな競合解消と、全体の競合を解決するグローバル競合解消とに二段階化している、競合解消処理とは、競合解消戦略に基づきインスタンシエーションの優先度を相互に比較し、最も優先度の高いものを選択する処理である。本方式では、まず各プロセッサがローカル競合解消により自プロセッサ内で最も優先度の高いインスタンシエーションを選択し、これをグローバル競合解消プロセッサに転送する。すべてのプロセッサからインスタンシエーションを受信したグローバル競合解消プロセッサは、全体で最も優先度の高いインスタンシエーションを選択する。プロセッサ内でのローカル競合解消には通信が不要であり、グローバル競合解消でも各プロセッサが一つのインスタンシエーションを転送するだけで良い。このため、各プロセッサが持つすべてのインスタンシエーションを一カ所に転送して競合解消を行う方式に比べ通信オーバヘッドを大幅に削減できる。グローバル競合解消は、最も早くローカル競合解消を終了したプロセッサ(図ではPE2)が行う。グローバル競合解消プロセッサの決定法については後述する。

グローバル競合解消プロセッサでは、インスタンシエーションが他のプロセッサから到着する毎に優先度を比較して、最優先のインスタンシエーションを選択しておく.この動作により、最も遅いプロセッサがインスタンシエーションを転送した後、一回の優先度比較でグローバル競合解消が終了する.したがって、全プロセッサの条件照合の終了を待って集中的に競合解消を行う方式に比べて、プロセッサのアイドル時間も削減される.

グローバル競合解消が終了すると、どのインスタンシエーションが選択されたかを全プロセッサに放送した後、同期を取り、実行フェーズに移行する。実行フェーズでも、アクション部に複数の WME 生成 / 更新 / 削除操作がある場合には、これを並列に処理する。選択されたインスタンシエーションを持つプロセッサが実行制御プロセッサ(図では PE1) となり、WME 生成 / 更新 / 削除命令を他のプロセッサに配布する。命令を受信したプロセッサは WME 操作を行い、処理が終了し

た時に終了通知を実行制御プロセッサに返送する.ただし,本方式での実行フェーズ並列化は,1回の認知-実行サイクルにつき1つのルールが実行される従来のプロダクションシステムの推論動作に従ったものであり,1回の認知-実行サイクルの中で複数のルールを並列実行するもの[40]ではない.

以上のように,本方式では条件照合フェーズのみでなく競合解消及び実行の各フェーズも並列処理し,また,各フェーズともローカリティの高い処理を抽出して並列化している.このため,通信が必要となるのは以下の場合だけである.

- 実行により発生したトークンの転送

- グローバル競合解消のためのインスタンシエーションの転送

- WME 生成 / 更新 / 削除命令と終了通知の転送

1回の認知-実行サイクルでの通信頻度は数回~10数回程度である.

## 3.2 ルール・WMEの割り付け法

ここでは,上述の通信が少ないという利点を保ったまま,負荷ばらつきを抑え,各プロセッサが持つローカルメモリが均等に消費されるような,ルール・WMEの割り付け法を提案する.

## 3.2.1 RETE サブネットの割り付け

冒頭でも述べたように,疎結合型並列コンピュータでは処理単位の実行中の異動は困難であるから,本方式ではルール条件部にあたるRETEサブネットを静的に割り付ける.

静的割り付けで良好な負荷バランスを達成するために,実行前にRETEサブネットの処理量を予測して,プロセッサでの処理量が均等となる割り付けを行う.正確な処理量は実際にESを動作させるまで知ることはできないが,処理量が活性化されるノード数に比例すると考えれば,RETEネットワークの構造からおおまかに予測することはできる.ルートノードに入力されたトークンは,クラスに応じてそのクラスに関係する定数テストノードへと流れ,定数テストに成功すればその下に接続された2入力ノードへ流れる.その2入力ノードでの照合が成功すれば更に下段の2入力ノードへと流れてゆく.このことから,定数テストノードで

の成功確率や2入力ノードでの成功確率を一定と近似すれば,活性化されるノード数は,活性化される定数テストノード数に比例すると考えられる.したがって,各プロセッサで活性化される定数テストノードの数を,どのクラスのトークンに対してもできるだけ均等になるようにRETEサブネットを割り付けることで,負荷の均等化を図る.以下に,割り付けアルゴリズムを示す.

#### 割り付けアルゴリズム

クラス  $C_1,C_2,\ldots,C_n$  を持つ RETE ネットワークを m 台のプロセッサ  $\mathrm{PE}_1,\mathrm{PE}_2,\ldots,\mathrm{PE}_m$  に割り付けることを考える .  $N_{ij}$  を ,  $\mathrm{PE}_j$  に割り付けられ , かつ , クラス  $C_i$  に関連する定数テストノードの数とすれば , クラス  $C_i$  に関連する定数テストノード数の分散  $V_i$  は ,

$$V_i = \frac{1}{m} \sum_{i=1}^{m} (N_{ij} - \frac{1}{m} \sum_{k=1}^{m} N_{ik})^2,$$

で表される.この分散がどのクラスに対しても小さくなるように,クラス毎の分散の総和,すなわち $V=\sum V_i$ を最小化する.そのために,以下の手順で RETE サブネットをプロセッサに割り付ける.

- 1. 分割された RETE サブネットを定数テストノード数の大きい順にソートする.

- 2. ソートされた RETE サブネットを一つ取り出す.

- $3. \ x$  を 1 から m まで変化させて, $PE_x$  にこのネットが割り付けられた場合の分散の和  $V=\sum V_i$  を計算する.

- 4. 上で計算した V が最も小さいプロセッサにネットを割り付ける.

- 5. すべての RETE サブネットを割り付けるまで,ステップ 2 からステップ 4 を繰り返す.

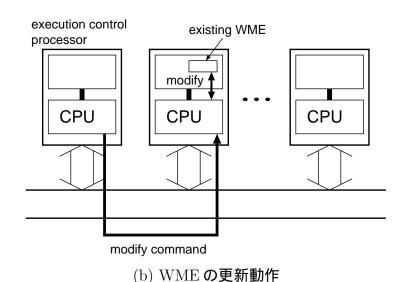

## 3.2.2 WMEの割り付け

WME 操作を並列に行い,かつ,各プロセッサでのメモリ消費を均等化するために WM も各プロセッサのメモリ上に均等に分散して配置する.

WME は WME 生成命令によって生成されるため,この生成命令の宛先プロセッサをランダムにすることで WME の分散を実現する.このように WME を分散した場合には,通信を抑えるために,WME 更新・削除動作は WME を保持するプロセッサが行う必要がある.

(a) WME の生成動作

図 3.2: WME 操作

以下にWME操作の詳細を述べる.図3.2(a) は WME生成動作を示している.アクション部に WME 生成記述がある場合には,実行制御プロセッサは他のいずれかのプロセッサに WME を生成命令を発行する.この WME 生成命令の宛先となるプロセッサをランダムに選択することにより WME は均等に分散される.一方,WME 更新 / 削除処理は,対象となる WME を持つプロセッサ上で行う.このために,インスタンシエーションにその WME を持つプロセッサの番号をタグとして持たせている.図3.2(b) に示すように,実行制御プロセッサがそのタグを参照して更新 / 削除命令を発し,WME を保持するプロセッサ上で実際の更新を行う.

# 3.2.3 アクション部の割り付け

上記の WM 割り付けでは,どのプロセッサでもあらゆるルールに記述された WME 操作を行う可能性があるため,ルールのアクション部はすべてのプロセッサに重複して割り付ける.実際には,アクション部は手続き型プログラムとして 表現されているので,このプログラムをすべてのプロセッサに配置する.アクション部のプログラムは RETE ネットワークや WME に比較してメモリ消費が十分小さいため,重複配置してもメモリ消費の総量はそれほど増加しない. $2 \sim 3$  の ES についての測定では,これによるメモリ消費増加は 10%程度である.

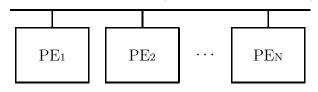

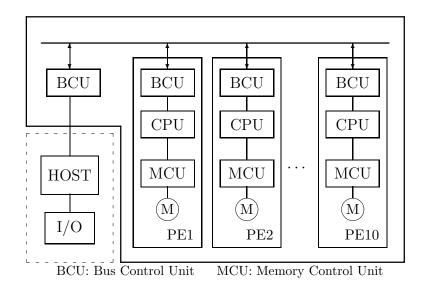

# 3.3 PS向け並列コンピュータ Presto

上記方式に基づいて推論インタプリタを並列処理すべく,並列コンピュータ "Presto"を開発した. Presto は,ローカルメモリと CPU とを持ったプロセッシン グエレメント (PE) をバスにより結合した疎結合型並列コンピュータである. PE 間の通信や同期はバスを介して行うが,ここに本並列化方式を効率的に処理する ための機能を持たせている.また,入出力はバスに接続されたホストプロセッサのみが行う.

ここでは Presto のハードウェア構成と,特徴的なバス機能について詳述する.

# 3.3.1 全体構成

Presto の構成を図 3.3 に示す.最大 10 台のプロセッサが BCU(Bus Control Unit)を介してバス結合されている.Presto は,NEC の PC9801 パーソナルコンピュータをホストプロセッサとし,そのバックエンドとして動作するよう設計されている.ホストプロセッサは,それが持つ拡張バス  $(C \ //\ /Z)$  からインタフェース回路を介して Presto のバスに接続される.このため,若干の回路的な差異があるものの,ホストプロセッサもバスで結合された一つの PE とみなすことができる.図 3.4 に,Presto をホストプロセッサに接続した様子を示す.

Presto そのものは,ディスクドライブ,ディスプレィ,キーボード,プリンタなどの入出力デバイスを持たない.このため,PEからの入出力は,すべてホストプロセッサを介して行うことになる.PE上には,MS-DOSシステムコールをインターセプトして,システムコール要求をホストプロセッサに転送する制御ソフ

図 3.3: Presto のハードウェア構成

図 3.4: ホストプロセッサに接続された Presto

図 3.5: Presto の PE 基板 (1 枚あたり 2PE)

トウェアが搭載される.これにより,PE上でも,MS-DOS 搭載の通常のパーソナルコンピュータと同じように入出力要求を処理することができる.PE上のアプリケーションソフトウェアからは,その PE上で入出力処理がなされているように見えるが,実際には入出力要求はホストプロセッサで処理される.このような機構により,すべての PE は,ホストプロセッサの制御下にあるあらゆる周辺デバイスを利用できることになる.

本論文で提案している PS 並列化方式は,プロセッサ間での処理の独立性が高く,通信オーバヘッドを抑えるよう工夫が加えられているため,このような低廉でコンパクトな並列コンピュータ上で効率的に実行することが可能である.

# 3.3.2 プロセッシングエレメント (PE)

個々の PE は , CPU とローカルメモリ , メモリ制御ユニット (MCU) , バス制御ユニット (BCU) から構成されている . ローカルメモリはバスを介して他の PE からもアクセスされるため , MCU はローカルメモリに対する CPU からのアクセス

とバスからのアクセスとの調停も行う、

Presto で用いられている PE の基板を図 3.5 に示す . 1 枚のプリント基板上に二つの PE を実装している .

# CPU:

CPU はインテル 80386 を用いた.ホストプロセッサである PC9801 も 80x86 を搭載しており,これと同一アーキテクチャの CPU を用いることで,開発環境を統一できる上,更に,ホスト OS と PE 上に搭載するモニタプログラム と間の親和性を高めることが容易にできる.更に,Presto のアプリケーションとして並列化の対象となる ES 開発ツール "KBMS" [31] 推論インタプリタ (KBMS/C) も,インテルアーキテクチャ上で動作するよう開発されている.このため,アーキテクチャの違いによる移植作業が不要となり,並列化に専念できる.

#### メモリ:

各 PE は最大で 4MB の DRAM を搭載する.Presto は各 PE がローカルメモリのみを持ち,共有メモリは持たない.メモリのリフレッシュやタイミング制御は,下に述べる MCU によって行われる.PE 間でのデータ転送は,ある PE のメモリにあるブロックデータを,MCU が BCU と連携して他の PE のメモリへ書き込むことにより行われる.すなわち,Presto でのプロセッサ間データ転送は DMA(Direct Memory Access) によるものであり,CPU の介在を必要としない.このために,メモリは,CPU だけでなくバス側から直接アクセスされる.なお,データ転送の詳細については,バス機能の項で述べる.

### BCU:

図 3.6 に BCU のブロック図を示す.BCU は, PE 間バス制御部, CPU バス制御部, DMA 制御部, 同期及び割込み制御部, バスアービタから構成されている.BCU は 10,000 ゲートの ASIC(Application Specific Integrated Circuit)チップ上で実現されている.

## MCU:

メモリの項で述べたように, MCU は, CPU 及びバス (BCU) からのメモリアクセスやリフレッシュを制御する.図3.7 にブロック図を示す. MCU は,

図 3.6: BCU のブロックダイヤグラム

CPU バス制御部,メモリアクセス制御部,メモリリフレッシュ制御部,データパス多重化部から構成されている. MCU は,5,000 ゲートの ASIC チップ上で実現されている.

# 3.3.3 バスの機能

ここでは、Prestoの特徴であるバスを用いたプロセッサ間通信機能を説明する、プロセッサ間通信とは、データ転送だけでなく、同期、割込み制御、バスアービトレーションも含む、

## データ転送

前述したように Presto におけるプロセッサ間のデータ転送は,ダイレクトメモリアクセス (DMA) によって行われる. DMA は,メモリと入出力サブシステム間のデータ転送を高速に行うために良く用いられる技術である. TWIN 方式では,プロセッサ間で転送されるデータは,連続したメモリブロックに配置されることが

図 3.7: MCU のブロックダイヤグラム

ほとんどである.このため,プロセッサ間のデータ転送においても,メモリブロックを CPU の介在なく転送できる DMA は効率的である.

本並列化方式においては,データ転送の要求が生じて DMA 転送が起動されるのは次のような場合である.

- 最初にローカル競合解消を完了したプロセッサがグローバル競合解消をする ために,他のプロセッサからそれぞれのプロセッサでのローカル競合解消結 果のインスタンシエーションを受け取る場合

- 実行フェーズにおいて,実行制御プロセッサが WME の生成/変更/削除のコマンドを発行する場合

- WME 操作により生じたトークンを全プロセッサに転送する場合

この DMA 機能は PE と PE の間の 1 対 1 データ転送だけではなく,ある PE からバス上のすべての PE に対してデータを一斉転送する放送モードも持つ. Presto において放送モードでのデータ転送が起るのは,上記の第 3 項,すなわちトークンを全 PE に転送する場合である.放送モードは条件照合のためにトークンを全 PE に繰返し転送するのに非常に効率的な方法である.

DMAでは、CPUの介在なしにデータが転送されるため、例えば条件照合フェーズにおいてはプロセッサが一つのトークンの処理を完了する前に別のトークンが送られて来る場合がある。同様に、実行フェーズでも、プロセッサがWMEの操作指示を処理し終わる前に次のWME操作指示が送られる場合もある。このような場合のデータ取りこぼしを防ぐために、二つのリングバッファが個々のPEに備わっており、それぞれ、トークンキューとアクションキューとして利用される。

また,デッドロックを防ぐために,各 PE にはシステム中の PE 数と同じ個数のデータ転送バッファが確保されており,更に PE 個数分のフラグレジスタが備えられている.フラグレジスタは,それぞれ対応する PE からセット/クリアができるようになっており,個々のデータ転送のフロー制御に使うことができる.PE は,自 PE が持つフラグレジスタのうち,送信先 PE に対応するフラグを参照し,これがクリアになっている場合にのみデータの送信を行う.例えば,PE $_x$  が PE $_y$  にデータを転送する場合,PE $_x$  は PE $_y$  の x 番目のバッファにデータを送り込むと同時に,自 PE 内の y 番目のフラグを立てる.データを受け取った PE $_y$  は,データ転送バッファ上のデータをその種別に応じて,トークンキューまたはアクションキーに移す.これをフラッシングと呼び,受信側の PE $_y$  の都合により任意のタイミングで実行される.フラッシングが済むと,PE $_y$  は送信側 PE $_x$  の y 番目のフラグを下す.

このように,データ転送個々のフロー制御をフラグレジスタを用いて行い,更にトークンや WME 操作指示に対してはキューを用意することで,デッドロックとデータの取りこぼしを回避している.

#### 同期

Prestoでは、PE間の同期のために2種類の機構が備えられている.一つは、専用の同期レジスタを用いた機構であり、もう一つは単純なワイヤード・アンド線による機構である.専用レジスタは柔軟なPE間同期を提供する.これは、レジスタ上の任意のパターンを同期条件として設定できるためである.一方、ワイヤード・アンド線による同期は高速であるが、単純な条件(全PEがこのワイヤード・アンド線をアサートした場合)でしか同期をとることができない.

個々の PE は同期レジスタを持っており、それぞれのレジスタの x 番目のビットが  $PE_x$  が同期待ち状態に入っていることを示すようになっている.この同期レジ

スタのx番目のビットは, $PE_x$ がバスの放送機能を使って全PEに対し一斉にセットすることができる.同期レジスタが指定したパターンとなった場合に,CPUに割り込みがかかるようになっている.

同期レジスタによる同期動作をより具体的に説明する. $PE_x$ , $PE_y$ , $PE_z$ の間で同期をとる場合を考える.これらすべての PE において,割り込み発生パターンとしてx 番目,y 番目,z 番目のビットがセットされた場合を指定しておく. $PE_x$  が自 PE が担当する処理を完了し,他の PE の完了を待つ同期待ちに入るとする.この際に, $PE_x$  は同期レジスタの x 番目のビットをセットするよう放送する.これより, $PE_x$  , $PE_y$  , $PE_z$  のすべての PE でそれぞれが持つ同期レジスタの x 番目のビットがセットされる.同様に, $PE_y$  が担当する処理を完了し,続いて  $PE_z$  の処理が完了したとする. $PE_z$  からの放送により,すべての PE で同期レジスタの x 番目,y 番目,x 番目のビットがセットされる.これによって,すべての x で同時に x で同期し込みが発生する.この割り込みによって同期待ち状態から次のフェーズへ移行するようにプログラムしておけば,これにより全 x で同期して次フェーズへ移行できる.

認知-実行サイクルにおいては,ローカル競合解消の後に同期が必要となる.このために本同期機構を利用している.各プロセッサはローカル競合解消を完了すると同期をとるための関数の呼び出して同期待ち動作に入る.すべてのプロセッサがローカル競合解消を完了すると,各 PE で CPU への割込みが発生し, PE は次のフェーズへ移る.

#### 割込み制御

PE は任意の PE に対して割込みをかけることができる.PE をまたがる割込みでは,PE 間でのメッセージ転送によって,ベクタ割込みと同様な動作を可能としている.PE は割込み要求ステータスレジスタを持っている.このレジスタは,割込みをかける先の PE がその割込み要求を受付けたがどうかを示すのに使われる.また,PE は割込み要求フラグを持ち,他の PE が割込み処理中であるかどうかを示すのに使っている.

${

m PE}_x$  が  ${

m PE}_y$  に対して割込みをかけることを考える.まず, ${

m PE}_x$  は割込み要求ステータスレジスタの y 番目のビットを調べる.もしこれがクリアされていれば,この y 番目のビットを立てた後に割込要求を  ${

m PE}_y$  に対して送る.もしも割込要求ス

テータスレジスタのビットがセットされていれば, $\mathrm{PE}_y$  は割込み処理中であることを示しているので,多重割込みによるデッドロックを防ぐために  $\mathrm{PE}_x$  から  $\mathrm{PE}_y$  への割込みは禁止される.

$PE_y$  では, $PE_x$  からの割込要求を受付けると,それを示すために割込要求ステータスレジスタの x 番目のビットをセットする.割込処理が完了すると, $PE_y$  は自身の x 番目のフラグと  $PE_x$  上にある割込要求ステータスレジスタの y 番目のビットをクリアする.結局, $PE_y$  はそれぞれの PE から一つの割込要求を受入れることができる.多重割込みによるシステムのデッドロックを防ぐため,個々の PE は,他の PE からの割込要求を一つずつしか受入れないようになっている.そして,PE 上ではこれら割込み要求をキューイングするようになっている.

割込要求は、あらゆるプロセッサ間通信において発生する.この割込要求は次の二つに分類できる.一つは、認知-実行サイクル中のデータ転送により発生する割込要求である.例えば、条件照合フェーズにおけるトークンの転送、ローカル競合解消の結果の転送、実行フェーズでの完了マークの転送などの際に発生する割込要求を含む.もう一方はより緊急性の高い割込要求である.この種の割込は、ローカル競合解消を最初に完了したプロセッサが、自分がグローバル競合解消を制御することを宣言する場合などに発生する.

#### バスアービトレーション

バスアービトレーション機能は、システム中で最も高位にある (PE 番号の若い)PE が担当する. VME バスにおけるアービトレーション [67] と同様に、バスを要求する PE はディジーチェイン接続されたグラント線によってバス利用の許可を受取る. 一般的にはディジーチェイン接続のグラント線を用いた方式はレスポンスタイムを増加させる. しかしながら、低廉で効率的であり、Presto のようなバス接続のマルチプロセッサシステムに対しては好適な方式である. アービトレーションサイクルを高速化するために、現在のバスマスタがバスサイクルを終了しなくとも、他のバスマスタ候補がバス要求を出すことが可能となっている.

# 3.4 推論インタプリタの実装

以下では,推論インタプリタの並列化をこのような並列コンピュータ上に実現 する場合の課題とその解決について述べる.

# 3.4.1 フェーズ移行処理

前述のように,本並列化方式では,条件照合フェーズの処理を非同期に行っている.このような非同期動作では,各プロセッサが,認知-実行サイクルで発生するすべてのトークンを処理したことをいかに判断するかが問題となる.1個のトークンの処理が完了した後も,いずれかのプロセッサでまだ WME 操作が行われていて,新たなトークンが発生する可能性があるためである.すべてのトークンが発生してしまい,それらに対する条件照合処理が完了したことを確認するまで,条件照合フェーズを終了することができない.

実行フェーズから条件照合フェーズへの移行に同期を挿入して,全プロセッサが実行終了を待てば確認は不要となるが,このような方法では,実行を早く終了したプロセッサのアイドル時間を増大させてしまう.本実現法では,常にどれか一台のプロセッサのみが実行フェーズを制御している点に着目し,実行終了を示す特殊なトークンを放送することにより,同期が不要な実行フェーズ終了確認を実現する.

各プロセッサはトークン用のキューを持ち,自プロセッサでの実行フェーズ終了直後からこのキューのトークンを取り出しながら条件照合処理を行う.キューが空の場合にも,いずれかのプロセッサでまだ WME 操作が行われており処理すべきトークンが到着する可能性があるため,キューの監視を続ける.実行制御プロセッサは,WME 操作を終了したプロセッサが発行する終了通知により実行フェーズ終了を確認すると,全プロセッサのトークンバッファに対して実行終了トークンを転送する.各プロセッサは,バッファから取り出したトークンが実行終了トークンであった場合にのみ,その認知―実行サイクルでの条件照合をすべて終了したと判断し,ローカル競合解消に移行する.

# 3.4.2 同期処理

競合解消フェーズから実行フェーズへの移行は,すべてのプロセッサが一斉に行う必要があるため,同期をとることが必要である.同期には,共有メモリに対してすべてのPEがプロセッサ状態を書き込み,各PEがこれを監視するポーリング方式が良く使われる.しかし,この方式では,監視のためのメモリアクセスが多数のPEから発生するためにバス競合が発生し,通信オーバヘッドの増大を招く.特にPrestoは共有メモリを持たないためこのような同期法は採ることができない.

Prestoでは、前述したようなバスの放送と特別なハードウェア(同期レジスタ)を用いて同期を実現する.同期レジスタは、PE台数分のビット長を持ち、バスからビット毎のセット/リセットが可能である.また、このレジスタが特定のパターンになった時に CPU に割り込みがかかるようにしている.各プロセッサは、競合解消が終了すると、バスの放送モードを利用して、全PE の同期レジスタに対し、自PE番号に対応するビットをセットする.そして、割り込みパターンを全ビットがセットされた状態に設定して、割り込み待ちに入る.全プロセッサで競合解消が終了した瞬間にすべての同期レジスタの内容は割り込み起動パターンと一致し、すべての PEで一斉に割り込みがかかる.この割り込みによって、全プロセッサが同時に実行フェーズに移行する.このように、バスの放送機能と論理演算可能なレジスタを利用して各 PE が独立かつ同時に同期検出を行うことにより、バスのトラフィックが少なくプロセッサにも負荷とならない同期が実現できる.

# 3.4.3 グローバル競合解消プロセッサの決定法

ローカル競合解消を最も早く完了したプロセッサが,グローバル競合解消プロセッサとなる.そのためには,全プロセッサが,他のプロセッサのローカル競合解消終了を同時に検出し,最も早く終了したプロセッサを識別する必要がある.本方式では,同期で用いたと同じ機能をもったレジスタを利用して,これを実現している.ローカル競合解消を終了したプロセッサは,まずこのレジスタをチェックする.どのビットもセットされていなければ,バスの放送モードを利用して,全PEのレジスタに自PEに対応するビットをセットする.このプロセッサがグローバル競合解消プロセッサとなる.一方,レジスタのどれかのビットがセットされていれば,既にローカル競合解消を終了したプロセッサが存在することになり,そのビットに対応するプロセッサがグローバル競合解消プロセッサである.この方式では,レジスタのチェックとビットのセットの間に,一度バスを解放するので,複数のPEでローカル競合解消が同時に終了した場合には,複数のビットがセットされる可能性がある.この場合にはPE番号の若いものをグローバル競合解消プロセッサとする.

# 3.4.4 認知-実行サイクルを通した動作

オーバヘッドとなり得る部分を以上のように処理することにより,並列化方式が本来持っている性能を十分に引き出すことが可能な実装となる.ここでは,本実装での,認知-実行サイクルを通した処理を追う.

個々のPEは,トークンキューとアクションキューという,二つの独立したキューを持つ.ルールの発火により生成されたトークンは,放送によりすべてのPEに送られトークンキューにプッシュされる.アクションキューは,WMEの生成,変更,削除などのWME操作要求を格納する.これらのWME操作要求は,ルール実行部の評価を行うPEが制御して送信する.

より詳細には,並列化された認知-実行サイクルは以下のようになる:

- 1. PE はトークンキューからトークンを 1 個取出し, TWIN 方式に基づいた条件 照合処理を行う.

- 2. もしも PE が直前の実行フェーズが完了したことを示す発火終了マークを見つけると,ローカルの競合集合から最も優先度の高いインスタンシエーションを選びだすローカル競合解消を行う.

- 3. 最初にローカル競合解消を終えた  $PE(以下この PE を PE_x と表す)$  は,他のすべての PE に対して割込みをかけ,その PE がグローバル競合解消を行うことを宣言する.他の PE は,各 PE ごとにその PE 内のローカル競合解消によって選択されたインスタンシエーションを  $PE_x$  に送信する.最も遅い PE が照合とローカル競合解消を終えてインスタンシエーションを送信するまで,他の PE は待つ.

- 4. グローバル競合解消の後,すべての PE は実行フェーズに移行する. $PE_x$  は,ルールのアクション部を評価し,アクション部にある WME 操作要求を,ランダムに選んだ PE のアクションキューに対して送り込む.それぞれの PE は,アクションキューから WME 操作要求を取出し,それぞれ処理する.

- 5. アクション部を評価し終えると, $\mathrm{PE}_x$  は発火終了マークを全  $\mathrm{PE}$  に対して送信する.

# 3.5 システムソフトウェア

推論インタプリタは,並列コンピュータである Presto にとってはアプリケーション・プログラムの一部である.アプリケーションがハードウェア資源を効率的に利用でき,不正な処理によってシステム全体が停止しないために,アプリケーションとハードウェアの中間層にシステムソフトウェアが存在する.ここでは,Prestoのシステムソフトウェアについて述べる.

すべての PE には同一のシステムソフトウェアがロードされる.システムソフトウェアの機能は,プロセッサ間通信,メモリ管理,ホストプロセッサ・エミュレーションに分類される.

## プロセッサ間通信

プロセッサ間通信機能には,データ転送,データ転送バッファのフラッシュ,同期,割込制御などがあり,3.3.3で述べたようなバス制御をシステムコールによって実現する.

# メモリ管理

メモリ管理機能としては,メモリ領域確保,メモリ領域開放,キューバッファの生成,キューバッファの削除がある.

### ホストプロセッサ・エミュレーション