(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4537942号 (P4537942)

(45) 発行日 平成22年9月8日(2010.9.8)

(24) 登録日 平成22年6月25日(2010.6.25)

(51) Int . CL.

HO4J 3/00 (2006.01)

HO4J 3/00

FL

Α

請求項の数 6 (全 19 頁)

(21) 出願番号 特願2005-342579 (P2005-342579) (22) 出願日 平成17年11月28日 (2005.11.28)

(65) 公開番号 特開2007-150744 (P2007-150744A)

(43) 公開日 平成19年6月14日 (2007. 6. 14) 審査請求日 平成20年2月5日 (2008. 2. 5) ||(73)特許権者 000004226

日本電信電話株式会社

東京都千代田区大手町二丁目3番1号

|(74)代理人 100121706

弁理士 中尾 直樹

(74)代理人 100066153

弁理士 草野 卓

(74)代理人 100128705

弁理士 中村 幸雄

(72) 発明者 守谷 健弘

東京都千代田区大手町二丁目3番1号 日

本電信電話株式会社内

|(72)発明者 原田 登

東京都千代田区大手町二丁目3番1号 日

本電信電話株式会社内

最終頁に続く

(54) 【発明の名称】信号多重化装置及び多重信号分離装置及びこれらの方法

#### (57)【特許請求の範囲】

### 【請求項1】

<u>減算器とアナログ積分器と量子化器とで構成される</u>オーバーサンプル低振幅分解能符号 化によって観測信号をディジタル信号とする複数の素子と、

上記複数の素子のディジタル観測信号を伝達する共通信号線と、

上記共通信号線に上記複数の素子のディジタル観測信号を時分割で出力させる制御部と

から構成され、

上記制御部は、素子ごとに設けられた素子制御部として構成され、各素子制御部は、前段に接続された逐次接続線からの出力指示信号に応答して上記複数素子よりのディジタル信号を上記共通信号線に出力すると共に、次段の素子に対し、出力指示信号を逐次接続線に送出するものであり、

<u>初段の素子制御部は上記オーバーサンプル低振幅分解能符号化のオーバーサンプリング</u>の1周期ごとに出力指示信号を生成するものであることを特徴とする信号多重化装置。

### 【請求項2】

請求項1に記載の信号多重化装置において、

上記制御部は素子ごとに設けられた素子制御部として構成され、各素子制御部は、

上記素子ごとに固有の識別番号の指示する時間を生成し、その時間に、当該ディジタル信号をそれぞれ上記共通信号線に出力するものであることを特徴とする信号多重化装置。

#### 【請求項3】

20

観測信号を減算器とアナログ積分器と量子化器とで構成されるオーバーサンプル低振幅 分解能符号化でディジタル信号化した複数の信号が時分割多重化されて伝送される共通信 号線と、

上記共通信号線上のディジタル信号を<u>上記オーバーサンプル低振幅分解能符号化の</u>オーバーサンプリングの1周期ごとに保持する保持信号を生成する制御部と、

その保持された信号をアナログ信号として復号する複数の素子と、

#### を備え、

上記制御部は素子ごとに設けられた素子制御部として構成され、各素子制御部は、前段 に接続された逐次接続線からの保持指示信号に応答して上記共通信号線上の信号を保持す るものであり、

<u>初段の素子制御部は上記オーバーサンプリングの1周期ごとに保持指示信号を生成する</u> ものであることを特徴とする多重信号分離装置。

#### 【請求項4】

請求項3に記載の多重信号分離装置において、

上記制御部は素子ごとに設けられた素子制御部として構成され、各素子制御部は、上記素子ごとに固有の識別番号の指示する時間を生成し、その時間に、上記共通信号線上の信号を保持するものであることを特徴とする多重信号分離装置。

### 【請求項5】

<u>減算器とアナログ積分器と量子化器とで構成される</u>オーバーサンプル低振幅分解能符号 化によって観測信号をディジタル信号とする複数の素子と、

上記複数の素子のディジタル観測信号を伝達する共通信号線と、

上記共通信号線に上記複数の素子のディジタル観測信号を時分割で出力させる制御部と

を備える信号多重化方法であって、

上記複数の素子が、減算器とアナログ積分器と量子化器とによオーバーサンプル低振幅 分解能符号化によって観測信号をディジタル信号とする過程と、

上記制御部は、素子ごとに設けられた素子制御部として構成され、その初段の素子制御部が、上記オーバーサンプル低振幅分解能符号化のオーバーサンプリングの1周期ごとに出力指示信号を生成し、上記初段の素子制御部以外の各素子制御部が、前段に接続された逐次接続線からの出力指示信号に応答して上記複数素子よりのディジタル信号を上記共通信号線に出力すると共に、次段の素子に対し、出力指示信号を逐次接続線に送出する過程と、

により信号を多重化する信号多重化方法。

#### 【請求項6】

観測信号を減算器とアナログ積分器と量子化器とで構成されるオーバーサンプル低振幅 分解能符号化でディジタル信号化した複数の信号が時分割多重化され<u>て伝</u>送される共通信 号線と、

上記共通信号線上のディジタル信号を<u>上記オーバーサンプル低振幅分解能符号化の</u>オーバーサンプリングの1周期ごとに保持する保持信号を生成する制御部と、

その保持された信号をアナログ信号として復号する複数の素子と、

## を備える多重信号分離方法であって、

上記制御部は素子ごとに設けられた素子制御部として構成され、その初段の素子制御部が、上記オーバーサンプリングの1周期ごとに出力指示信号を生成し、上記初段の素子制御部以外の各素子制御部が、前段に接続された逐次接続線からの保持指示信号に応答して

<u>上記共通信号線上の信号を保持する過程</u>により<u>上記</u>共通信号線上の信号を分離する多重信号分離方法。

【発明の詳細な説明】

### 【技術分野】

## [0001]

この発明は、多数の観測信号を少ない伝送線で伝送する技術に関する。例えば多数のマ

20

10

30

30

40

10

20

30

40

50

イクロホンによって収音した音響信号を少ない配線数で伝送する信号多重化装置及び、その多数の音響信号を多数のスピーカーで再生するために多重化された信号を分離する多重信号分離装置、及びそれらの装置を用いて例えば収音した音場を他の場所に忠実に再現することが出来るような方法に関する。

### 【背景技術】

#### [0002]

自然界の事象を電気的に検出してその信号を伝送するに当たっては、雑音余裕度を向上させる目的でアナログ信号である観測信号をそのまま伝送するのでは無く、一度、そのアナログ信号をディジタル信号に変換(Analog to Digital Conversion、以降 A / D 変換と称する)してから伝送する方法がある。

AD変換については、従来からアナログ信号を一定値に保持して、振幅方向の分解能を例えば8bit若しくは16bit程度確保する逐次比較型AD変換器が良く用いられていた。この方法でAD変換を行うと、信号の振幅の精度を得ようとすると多bit化が前提になり、そのディジタル化した信号を伝送するためには、少なくとも多bitに対応した複数の信号線を必要とする課題があった。また、振幅方向の精度を高めるためには、アナログ信号

号線を必要とする課題があった。また、振幅方向の精度を高めるためには、アナログ信号を一定時間の間、一定値に保持する必要があり、その結果、変換に時間がかかり変換速度が遅く、、また回路規模が大きくなる課題があった。

特に多数の信号をAD変換する場合、例えば、多数のマイクロホンそれぞれについて逐次比較型AD変換器でディジタル信号に変換するのは、回路規模が大きく、非常にコストの高いものになる課題があった。

#### [0003]

このような課題を持つ逐次比較型 A D 変換器に対して、サンプリング周波数をナイキスト周波数よりも十分高い周波数で行い、時間方向の分解能を上げることで、高い S / N 比を得る オーバーサンプル低振幅分解能符号化技術による A D 変換器を用いる方法がある。 オーバーサンプル低振幅分解能符号化技術による A D 変換器は、エイリアシングフィルタ等のアナログ回路がディジタル化出来ること、及びアナログ量をディジタル量に変換する量子化部や D A 変換部が 1 ~数bitで回路化できるので、低コスト化、低消費電力化が図れる。

### [0004]

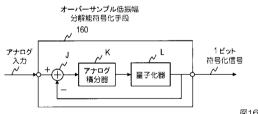

図16にオーバーサンプル低振幅符号化技術による1bit A D 変換器の例を示し、その動作を簡単に説明する。1bit A D 変換器160は、減算器Jとアナログ積分器 K と量子化器 L とによって構成される。減算器Jでアナログ入力と量子化器 L の出力とを減算し、アナログ入力が増加方向に変化している場合には、量子化器 L は正極性のパルスを出力する。アナログ入力が減少方向に変化すると量子化器 L は負極性のパルスを出力する。アナログ入力値が変化しない場合は、量子化器 L は正と負のパルスを交互に出力する。サンプリング周波数(パルス間隔)を2~3MHz程度とすることによりアナログ入力信号の波形を忠実にAD変換することが出来る。

#### [0005]

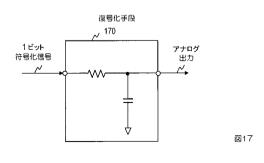

図17に1bit A D変換器でディジタル化された信号をアナログ信号に復号する復号化手段を示す。1bit A D変換器が上記したようなアルゴリズムで1bitの符号化信号を生成するものであるから、復号化手段170は、図17に示すように低域通過フィルタで構成することができる。つまり、正極性のパルスが連続して入力される時のアナログ出力信号は、階段状に上昇し、正と負のパルスが交互に入力されるとアナログ出力信号は現状の値を維持し、負極性のパルスが連続して入力されると、アナログ出力信号はゼロに向かって減少し、更に負極性のパルスが入力されると、アナログ出力信号は負極性に至る。このようにして1bit A D変換器のディジタル信号はアナログ信号に復号される。このようなオーバーサンプル低振幅符号化技術を用いることで、少ない信号線(1~数bit)でアナログ信号を伝送することが可能になる。

### [0006]

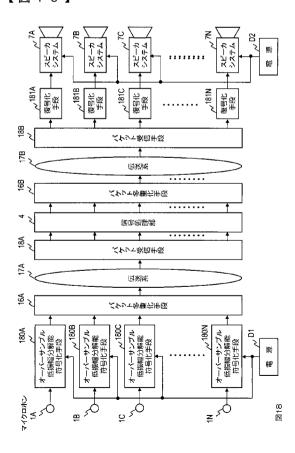

このオーバーサンプル低振幅符号化技術を用い、発明者らが提案した多チャネル音響信

号を低コストで伝送する多チャネル符号化装置を図18に示す。N本のマイクロホン(1A~1N)からのアナログ信号のそれぞれを、オーバーサンプル低振幅分解能符号化手段180A~180NでA/D変換する。A/D変換された各マイクロホンの信号が入力されるパケット多重化手段16Aでは、各マイクロホンを識別する識別信号をA/D変換器の出力信号に付し、小さなまとまりのデータ、つまりパケット(packet)化した上に更に多重化して伝送系17Aに送出する。(パケット受信手段18Aから伝送系17Bの説明は、以下の説明と同じであるので省略する)

パケット受信手段 1 8 B は、そのパケット化されたマイクロホンの信号を受信し、パケット信号内の識別信号に応じて、識別信号に対応した復号化手段 1 8 1 A ~ 1 8 1 N にマイクロホンの信号を供給する。復号化手段 1 8 1 A ~ 1 8 1 N は、図 1 4 で説明済みの動作を行いアナログ信号に復号化し、復号化手段 1 8 1 A ~ 1 8 1 N それぞれに接続されたスピーカーシステム 7 A ~ 7 N で音響信号に変換されて出力される。

#### [0007]

また、従来から複数のチャネル信号を時分割多重する場合は、その複数のチャネル信号を一箇所に集約し、各チャネル信号を同期信号の1周期間に設けられた複数のタイムスロットの各1つに順次割り当てて送出する方法が一般的であった。そうして多重化された時分割信号の分離も一箇所で行っている。

このように従来においては、パケット多重化、時分割多重化のいずれでも各チャネル信号を一箇所に集約しているため、多重化装置と各信号線間の配線が複雑になっていた。多重分離においても同様であった。

【特許文献1】特開2004-191545(図4)

#### 【発明の開示】

【発明が解決しようとする課題】

#### [00008]

しかしながら、上記したような従来の技術では、例えば、逐次比較型 A D 変換器を用いる場合よりは、オーバーサンプル低振幅符号化技術を用いているので、その分、伝送系の信号線を少なくすることが出来るが、オーバーサンプル低振幅符号化技術を用いた特徴を十分生かしているとは言えなかった。つまり、パケットによる多重化は、パケットのヘッダに記述されるアドレスによって個々のマイクロホンやスピーカー素子を識別する必要があり、数多くの素子の信号を多重化するには伝送速度の限界がある。また、個々のデータが大きくなるので多重化できるチャネル数も減少してしまう。

## [0009]

この発明はこのような点に鑑みてなされたものであり、オーバーサンプル低振幅符号化技術の特徴を生かして、構成が簡単で、伝送系の信号線の数が少なく、また高速な信号伝達が可能な多重化装置及び多重信号分離装置を提供することを目的とする。

【課題を解決するための手段】

## [0010]

この発明の信号多重化装置は、オーバーサンプル低振幅分解能符号化によって観測信号をディジタル信号とする複数の素子と、その複数の素子からのディジタル出力信号を時分割で共通信号線に多重化出力させる制御部とからなる。

更に、この発明の多重信号分離装置は、時分割多重化され、共通信号線に出力されたディジタル信号をオーバーサンプリングの1周期ごとに保持する複数の保持信号を生成する制御部と、その保持された信号をアナログ信号として復号する複数の素子とからなる。

## 【発明の効果】

#### [0011]

以上のようにこの発明の信号多重化装置及び多重信号分離装置によれば、伝送系の信号線をオーバーサンプル低振幅符号によってディジタル化された少ない信号線(1~数bit の共通信号線)で形成することから、個々の伝送信号に識別信号を必要としない、低コストで高速な時分割多重伝送が実現できる。

### 【発明を実施するための最良の形態】

10

20

30

40

#### [0012]

以下、この発明の装置の実施の形態を図面を参照して説明するが、その動作説明により、発明の方法の実施形態の説明も兼ねる。以降の説明において、同一のものには同一の参照符号を付け、説明は繰り返さない。

### 「第1の実施の形態]

### 「実施例1]

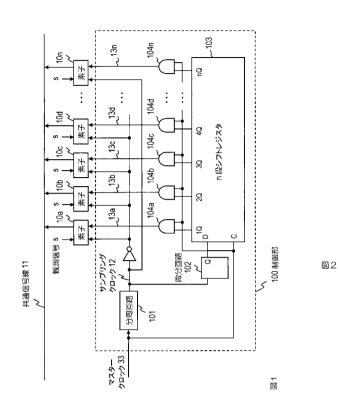

図1にこの発明による信号多重化装置の実施例1を示す。観測信号Sをオーバーサンプル低振幅分解能符号化でディジタル信号化する複数の素子10a~10nのA/D変換出力が、共通信号線11にそれぞれ接続されている。複数の素子10a~10nをそれぞれ活性化させるサンプリングクロック12と、素子の出力である観測信号のA/D変換結果を、共通信号線11に時分割で出力させるゲート信号13a~13nが制御部100から供給されている。

#### [0013]

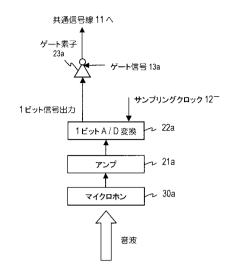

素子の一例を図 2 に示す。図 2 は、観測信号として音を検出するマイクロホン 3 0 を用いた素子 1 0 a ~ 1 0 n の一つを示す。素子 1 0 a は、マイクロホン 3 0 a と 1 bit オーバーサンプル型 A / D 変換器 2 2 a とゲート素子 2 3 a を一体化したものである。音波をマイクロホン 3 0 a で電気信号に変換し、その電気信号をアンプ 2 1 a で増幅し、その増幅された信号を、制御部 1 0 0 からのサンプリングクロックが " 1 " (論理レベル 1 を意味する)のタイミングで 1 bit A / D 変換器 2 2 a によってオーバーサンプリング低振幅分解能ディジタル信号に A / D 変換する。制御部 1 0 0 からのゲート信号が " 1 " のタイミングでゲート素子 2 3 a が制御され、 A / D 変換されたディジタル信号が共通信号線 1 1 に出力される。

#### [0014]

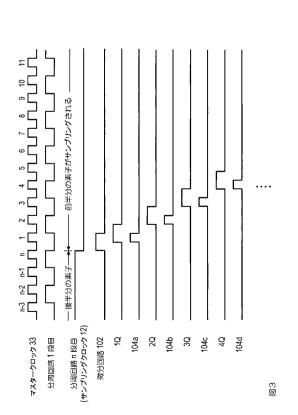

制御部100の動作タイムチャートを図3に示し、その動作を説明する。制御部100は、マスタークロック33の立下りのタイミングで動作するn段の分周回路101の最終分周出力信号を、サンプリングクロック12として各素子10a~10nに供給する。素子10a~10nの前半の半分には、分周回路101の最終分周出力信号を反転させたサンプリングクロック12 (記号A はAの反転を意味する)が供給され、後半の半分には分周回路101の最終分周出力信号がそのまま供給されている。つまり、サンプリングクロック12が"0"の期間で前半分の素子10a~10\*(\*は素子全数の半分の数に対応した符号である)がサンプリングされ、"1"の期間で残り半分の素子がサンプリングが応した符号である)がサンプリングされ、"1"の期間で残り半分の素子がサンプリングオに、オーバーサンプリング状態で1bit A/D変換器22aが動作する。

### [0015]

各素子10a~10nのA/D変換結果であるディジタル出力信号を共通信号線11に出力するタイミングを決定するゲート信号13a~13nは、分周回路101の最終分周出力(n段目)の立下りのタイミングでマスタークロック33の一周期分の時間幅のパルス信号を生成する微分回路102と、微分回路102の出力するパルス信号をマスタークロック33の立ち上がりのタイミングでシフトさせるn段のシフトレジスタ103と、シフトレジスタ103の各段の出力とマスタークロック33との論理積を取るANDゲート104a~104nとによって生成される。

#### [0016]

サンプリングクロック 1 2 の周波数を例えば 2 M H z とし、素子の数を n 個とすると、マスタークロック 3 3 は、 n × 2 M H z の周波数に設定される。微分回路 1 0 2 は、分周回路 1 0 1 の最終分周出力信号の立下りのタイミングで、マスタークロック 3 3 の 1 周期分の時間幅を持つパルスを周期的に発生する。微分回路 1 0 2 が発生したパルスは、 n 段のシフトレジスタ 1 0 3 に入力され、マスタークロック 3 3 の 1 周期の時間幅で 1 周期の時間ずつ遅れた(シフトされた)信号に変換される( 1 Q , 2 Q , 3 Q , ・・・)。

このマスタークロック 3 3 の 1 周期分ずつシフトされた n 段シフトレジスタ 1 0 3 の各段の出力信号と、マスタークロック 3 3 との論理積で各素子のゲート信号が生成される。

10

20

30

40

10

20

30

40

50

素子 1 0 a のゲート信号 1 3 a は、 A N D ゲート 1 0 4 a によってマスタークロック 3 3 のクロック 1 のタイミングに発生する。素子 1 0 b のゲート信号 1 3 b は、 A N D ゲート 1 0 4 b によってマスタークロック 3 3 のクロック 2 のタイミングに発生する。

### [0017]

以下同様にn個の素子に対するn個のゲート信号がそれぞれ異なるタイミングに発生される。この結果、各素子10a~10nで検出された音波は、共通信号線11上に時分割多重される。

このようにこの発明の信号多重化装置によれば、複数の素子に個別の識別信号を付する 事も無く、最小の信号線で、且つ高速な信号の伝送を行うことが可能になる。また、この 共通信号線11上の時分割多重信号には、同期信号が含まれていない。

#### 「実施例21

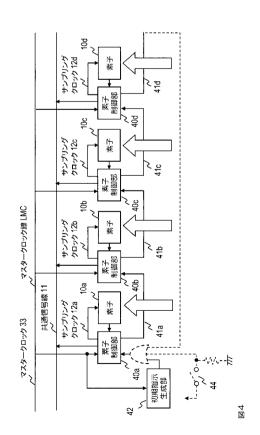

制御部として素子ごとに素子制御部を設け、素子を制御する配線数も減らした実施例 2 を図 4 に示す。各素子 1 0 a , 1 0 b , 1 0 c , 1 0 d ごとに素子制御部 4 0 a , 4 0 b , 4 0 c , 4 0 d が設けられ、各素子 1 0 a ~ 1 0 d には、各素子制御部 4 0 a ~ 4 0 d からサンプリングクロック 1 2 a ~ 1 2 d が供給されている。各素子制御部 4 0 a ~ 4 0 d は前段の素子制御部からの逐次接続線 4 1 a ~ 4 1 c によって芋づる式に順次接続されている。初段の素子 1 0 a の素子制御部 4 0 a には、初期指示生成部 4 2 が接続されている。初期指示生成部 4 2 及び各素子制御部 4 0 a ~ 4 0 d には、マスタークロック線 L M C からそれぞれマスタークロック 3 3 が供給されている。各素子 1 0 a ~ 1 0 d の出力は、各素子制御部 4 0 a ~ 4 0 d を介して共通信号線 1 1 に接続されている。図 3 は、素子が 4 個の例を示しているが、同じ接続関係で n 個接続することが可能である。

#### [0018]

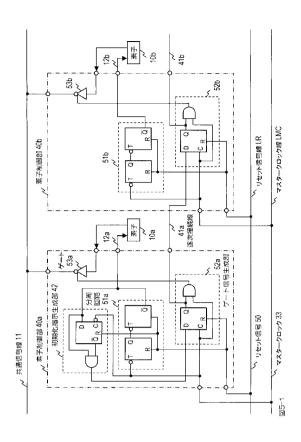

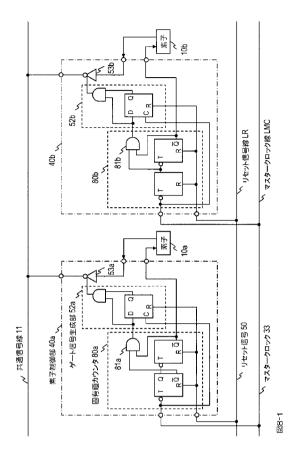

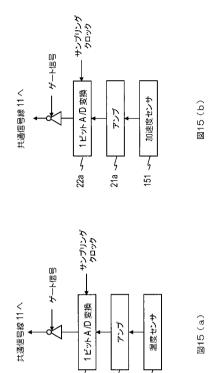

図5(作図上の都合により図5 - 1と図5 - 2に分かれているが、本来1個の物である)に実施例2をより具体的に示す。図5は図4に対して回路を初期化するためのリセット信号50を各素子制御部に送るリセット信号線LRが追加されているが、他の構成は図4と全く同じである。リセット信号50は、図5に用いられているT型フリップフロップ(Toggle type Flip Flop以降、TFFと称す)とD型フリップフロップ(Delay type Flip Flop以降、DFFと称す)の全てのリセット端子に接続され、回路全体を初期化するものである。動作停止時に"1"(初期化)、動作時に"0"とされる信号である。各素子10a~10dを制御する素子制御部40a~40dには、素子制御部自身がサンプリングクロックとゲート信号を生成する目的で、分周回路51a~51dとゲート信号生成部52a~52dとゲート素子53a~53dがそれぞれに設けられている。なお、図2の説明では、ゲート素子23a~23nが各素子に一体化された例で示したが、図5においては、そのゲート素子23a~53dとして素子制御部側に組み込んだ構成で示している。動作に変わりはない。初段の素子10aを制御する素子制御部40aだけに、初期化指示生成部42が設けられている。

## [0019]

各素子制御部  $40a \sim 40d$  は、それぞれが生成するサンプリングクロック  $12a \sim 12d$  を各素子  $10a \sim 10d$  に供給すると共に、各素子からのディジタル信号をゲート素子  $53a \sim 53d$  を介して共通信号線 11 に出力する。各素子制御部同士は、逐次接続線で接続される。素子制御部 40a と 40b が逐次接続線 41a で、素子制御部 40b と 40c が逐次接続線 41b で、素子制御部 40c と 40d が逐次接続線 41c で接続されている。この実施例の最終段の素子制御部 40d には、逐次接続線 41d が接続されていない。

## [0020]

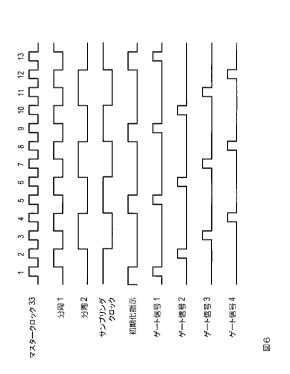

図 5 の動作を示すタイムチャートを図 6 に示し、動作を説明する。各素子制御部 4 0 a ~ 4 0 d から各素子 1 0 a ~ 1 0 d に供給されるサンプリングクロックの周波数を 2 M H z とした場合、マスタークロック 3 3 の周波数は 4 倍の 8 M H z である。

各素子制御部40a~40d内のTFF2段で構成された分周回路51a~51dは、マスタークロック33の周波数をT端子に入力されるクロック信号の立下りで分周し、各

素子へ供給するサンプリングクロック  $1\ 2\ a\sim 1\ 2\ d$  を生成する。素子  $1\ 0\ a$  と素子  $1\ 0$  のサンプリングクロック  $1\ 2\ a$  、  $1\ 2\ b$  と、素子  $1\ 0\ c$  と素子  $1\ 0\ d$  のサンプリングクロック  $1\ 2\ c$  、  $1\ 2\ d$  の位相は  $1\ 8\ 0$  。異なっている。つまり、それぞれ同一の構成の分周回路を構成する最後のTFFの異なる極性の出力がサンプリングクロックとされている。素子  $1\ 0\ a$  、  $1\ 0\ b$  のサンプリングクロックがTFFのQ 、素子  $1\ 0\ c$  、  $1\ 0\ d$  のサンプリングクロックがTFFのQ端子から取られている。したがって、リセット信号  $1\ 0\ c$  の  $1\ 0\ c$  がサンプリングされ、次に素子  $1\ 0\ c$  と  $1\ 0\ c$  がサンプリングクロックによって交互に素子  $1\ 0\ a$  、  $1\ 0\ b$  と、素子  $1\ 0\ b$  、  $1\ 0\ c$  が活性化される。

### [0021]

初段の素子10aを制御する素子制御部40aには、分周回路51aの最後のTFFのQ の立ち上がりでパルスを発生させる微分回路で構成された初期化指示生成部42が設けられている。初期化指示生成部42は、分周回路51aの最後のTFFのQ の立ち上がりでマスタークロック33の一周期分の幅の初期化指示パルスを、サンプリングクロック(分周回路51aの最後のTFFのQ)の立下りのタイミングで周期的に発生する。

その初期化指示パルスは、ゲート信号生成部 42a を構成する DFFの D端子に入力され、マスタークロック 33 の半周期分遅らされた DFF $_{52a}$  の Q出力とマスタークロック 33 との論理積を取るアンドゲート  $G_{52a}$  によって、ゲート信号 1 となる。ゲート信号 1 は、素子 10a のディジタル出力信号の共通信号線 11 への接続を制御するゲート素子 10a のコントロール端子に接続されている。

### [0022]

ゲート信号生成部 5 2 a を構成する D F F <sub>5 2 a</sub>の Q 出力は、初期化指示パルスをマスタークロック 3 3 の半周期分遅らせた信号、図 6 においてマスタークロック 3 3 のクロック 1 の立ち上がりからクロック 2 の立ち上がりまでのパルスである。このパルスが、次段への出力指示信号として逐次接続線 4 1 a によって素子制御部 4 0 b に供給される。

逐次接続線 4 1 a によって、供給される出力指示信号は、素子制御部 4 0 b のゲート信号生成部 5 2 b を構成する D F F  $_{5 2 b}$  の D 端子に入力される。 D F F  $_{5 2 b}$  の Q 出力は、マスタークロック 3 3 のクロック 2 の立ち上がりで " 1 " (論理レベル 1 ) になり、次のクロック 3 の立ち上がりのタイミングで " 0 " に変化する。 つまり、素子制御部 4 0 a からの出力指示信号がマスタークロック 3 3 の 1 クロック 3 3 の 1 クロック 6 遅れた D F F  $_{5 2 b}$  の Q 出力とマスタークロック 3 3 との論理積を取るアンドゲート G  $_{5 2 b}$  によって、ゲート信号 2 が生成される。ゲート信号 2 は、素子 1 0 b のゲート素子 5 3 b のコントロール端子に接続されている。

### [0023]

以降同様に、素子制御部40cは、マスタークロック33のクロック3の立ち上がりからクロック4の立ち上がりまで"1"となる出力指示信号を生成し、マスタークロック33のクロック3のタイミングで"1"となるゲート信号3を生成する。

素子制御部40dは、マスタークロック33のクロック4の立ち上がりからクロック5の立ち上がりまで"1"となる出力指示信号を生成し、マスタークロック33のクロック4のタイミングで"1"となるゲート信号4を生成する。

図5は、素子が4個しかない例であるので、4段目の素子制御部30dからの出力指示信号は、開放されているが、上記した関係で以降n個の素子及びn個の素子制御部を接続することが可能である。その場合、マスタークロック33の周波数をサンプリングクロックの周波数の少なくともn倍にすれば良い。

#### [0024]

以上説明した図5の動作を整理して述べると、マスタークロック33が"0"の期間、素子10aと10bが活性化(サンプリング)され、反対の"1"の期間は、素子10cと10dが活性化される。その状態において、素子10aのディジタル出力信号がマスタークロック33のクロック1,5,9のタイミングで共通信号線11に出力され、素子10bはクロック2,6,10、素子10cはクロック3,7,11、素子10dはクロック4,

10

20

30

40

8,12のタイミングで共通信号線11に出力される。この動作はマスタークロック33が発生している間繰り返されるので、共通信号線11を通して、各素子10a~10dで 観測したディジタル出力信号を多重化して伝送することが可能になる。

#### [0025]

以上説明した実施例2は、図1に示した実施例1に対して、素子ごとに素子制御部を設けたことにより、素子制御のための長い配線を減らす効果がある。実施例1では、n個の素子に対してそれを制御する制御部100が1個であるために、それぞれを制御するための配線数を多く必要としていた。実施例2によればn個の素子に対して、共通信号線と初期化するためのリセット信号線LRとマスタークロック線LMCと、各素子制御部間を接続する逐次接続線41の4系統の信号線(配線)のみで構成することが出来る。

なお、この実施例2の最後の素子制御部40dからの逐次接続線41dが無い形で説明を行ったが、図4に破線で示すように素子制御部40dからの逐次接続線41dを初段の素子制御部40aに接続しても良い。このように素子制御部を逐次接続線で円環状に接続することも可能である。その場合、初期指示生成部42が簡単なスイッチに置き換え可能である。図4に破線で示すスイッチ44を一定時間(短い時間でよい)オンさせて素子制御部40aにゲート信号を発生させると、後は、逐次接続線41a~41dを介して順次、各素子制御部が上記した動作を行う。

#### 「実施例31

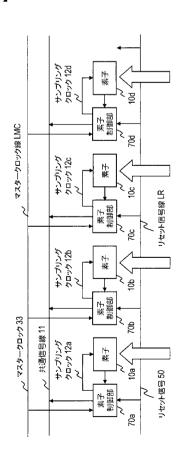

更に素子を制御する配線を減らした実施例3を図7に示す。図7は実施例2で示した各素子制御部内に設けられた分周回路を固有値カウンタに置き換えた素子制御部70a~70dとすることで、各素子制御部間を芋づる式に接続する逐次接続線を無くしたものである。その部分が異なるだけで他の構成は全く同じであるので、図7の説明は省略し、図7を具体的に構成した一例を示す図8について説明する。

#### [0026]

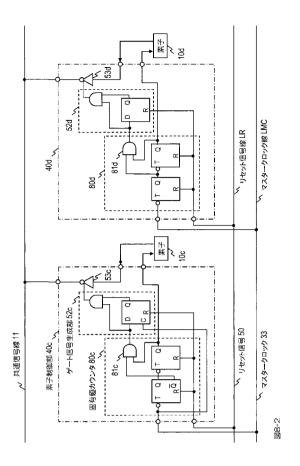

図8(作図上の都合により図8-1と図8-2に分かれているが、本来1個の物である)は、実施例2と同様に素子が4個の例で示す。説明済みの実施例2と異なる点は、各素子制御部40a~40d内の分周回路51a~51dが、固有値カウンタ80a~80dに置き換わっている点だけが異なっている。

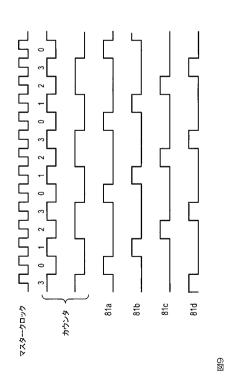

固有値カウンタ80a~80dの構成は、単純な2bit(この例では素子が4個なので22bitである)のバイナリーカウンターで構成され、各カウンタがそれぞれの固有値でキャリーを発生させるようにデコーダ81a~81dを有している。図9にその動作タイムチャートを示す。素子制御部40aの固有値カウンタ80aに設けられたデコーダ81aは、ANDゲートで構成され固有値カウンタのカウント値が0の期間"1"となるパルスを発生させ、ゲート信号生成部52aに供給する。

### [0027]

素子制御部40bでは、固有値カウンタのカウント値が1の期間"1"となるパルスを発生させ、ゲート信号生成部52bに供給する。以降同様にカウント値2の期間が素子10c、カウント値3の期間が素子10dのタイミングとなる。

この各固有値カウンタ80a~80dが生成するパルスは、実施例2で示した逐次接続線41a~41cによって次段の素子制御部へのゲート信号生成のタイミングを指示する信号と同じものである。

このように各素子制御部内に固有値カウンタを設けることで、実施例2で示した逐次接続線も無くすことが可能になる。この結果、共通信号線11とリセット信号線LRとマスタークロック線LMCの3本の配線だけで、n個の素子の信号を時分割多重伝送することができる。この例では、素子を4個の例で説明したが、素子の数を増やしても固有値カウンタ80a~80dのカウント値を増やすだけの変更で、この発明を実施することが出来る。

### [0028]

以上述べたような構成において、オーバーサンプル低振幅分解能符号化によって複数の 観測信号をディジタル化する過程と、そのディジタル化した複数の観測信号を共通信号線 10

20

30

40

(9)

に時分割で出力する過程を実行することで、信号多重化方法が実現できる。

#### [第2の実施の形態]

### 「実施例1]

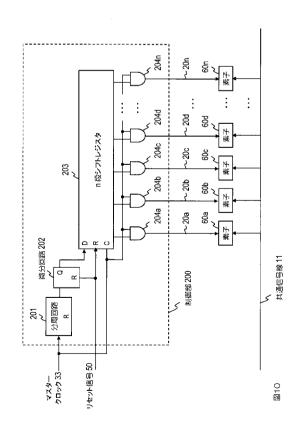

図10にこの発明による多重信号分離装置を示す。観測信号をオーバーサンプル低振幅分解能符号化でディジタル信号化した複数の信号が伝送される共通信号線11に、ディジタル信号をアナログ信号に復号するn個の素子60a~60nが接続されている。各素子には、制御部200から共通信号線11上に多重化されたディジタル信号をオーバーサンプリングの1周期ごとに保持するための保持信号20a~20nが、それぞれ供給されている。

### [0029]

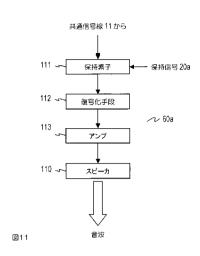

素子 6 0 a ~ 6 0 n の一例を図 1 1 に示す。図 1 1 は、例えばスピーカー 1 1 0 を用いた素子 6 0 a ~ 6 0 n の一つを示す。素子 6 0 a は、制御部 2 0 0 から供給される保持信号 2 0 a によって共通信号線 1 1 上のディジタル信号を保持する保持素子 1 1 1 と、保持素子 1 1 1 で保持したディジタル信号をアナログ信号に復号する復号手段 1 1 2 と、復号手段 1 1 2 の出力信号を増幅してスピーカー 1 1 0 に供給するアンプ 1 1 3 とで構成される。

復号手段112については、背景技術で説明した図14と同じものであるので、説明を 省略する。このように素子60aを構成することで、オーバーサンプリング周波数の周期 でディジタル化された例えば音波を再生することが可能である。

### [0030]

制御部200の動作が図3で説明した信号多重化装置の実施例1の動作とほとんど同じである。したがってタイムチャートは図3を参照されたい。図3の微分回路102が202、ANDゲート104aが204aに相当する。制御部200は、マスタークロック33の立下りのタイミングで動作するn段の分周回路201と、最終分周出力の立下りのタイミングでマスタークロック33の一周期分の時間幅のパルス信号を生成する微分回路202と、微分回路102の出力するパルス信号をマスタークロック33の立ち上がりのタイミングでシフトさせるn段のシフトレジスタ203と、シフトレジスタ203の各段の出力とマスタークロック33との論理積を取るANDゲート204a~204nとで構成される。

### [0031]

微分回路 2 0 2 は、分周回路 2 0 1 の最終分周出力信号の立下りのタイミングで、マスタークロック 3 3 の 1 周期分の時間幅を持つパルスを周期的に発生する。微分回路 2 0 2 が発生したパルスは、 n 段のシフトレジスタ 2 0 3 に入力され、マスタークロック 3 3 の 1 周期の時間幅で 1 周期の時間ずつ遅れた(シフトされた)信号に変換される( 1 Q , 2 Q , 3 Q , ・・・)。

このマスタークロック33の1周期分ずつシフトされたn段シフトレジスタ203の各段の出力信号とマスタークロック33との論理積で各素子の保持信号が生成される。素子60aの保持信号は、ANDゲート204aによってマスタークロック33のクロック1のタイミングに発生する。保持素子111はDFF等で構成されるラッチ回路であり、例えば保持信号が"1"の時に読み込み"0"に変化する瞬間の共通信号線11上の信号を保持するものである。素子10bのゲート信号は、ANDゲート204bによってマスタークロック33のクロック2のタイミングに発生する。

### [0032]

以下同様にn個の素子に対するn個の保持信号がそれぞれ対応するタイミングで共通信号線11に出力されたディジタル信号を保持する。したがって、共通信号線11にオーバーサンンプリング低振幅分解能符号化によってディジタル化され、多重化された信号多重化装置と同じマスタークロック周波数及び、初期動作を同時に開始させれば、上記した構成により多重信号分離が可能である。初期動作を同時に開始させるのは、信号多重化装置側のリセット信号と同じリセット信号を多重分離装置側でも用いるようにすれば容易に行える。

10

20

30

#### [0033]

なお、上記した例では、共通信号線11上にマイクロホン側の信号が出力されるタイミングと、多重分離装置側の保持回路が共通信号線11上の信号を保持(ラッチ)するタイミングが一致しているように見えるが、一般的には保持信号の立下りのタイミングの方が、共通信号線11上のデータが不定になるより早いため確実に保持することが可能である。この辺りの遅延による動作が心配の場合は、マスタークロックよりも高い周波数の信号を用いて保持信号を生成するようにすれば良く、タイミング上の余裕を確保することは容易であり設計上の問題である。

### [0034]

また、この発明の説明のために示した具体的な回路についても、あくまでも一例であり、例えば固有値カウンタ等は、その設計方法によって種々の変形が可能なことは言うまでも無いことである。

#### [実施例2]

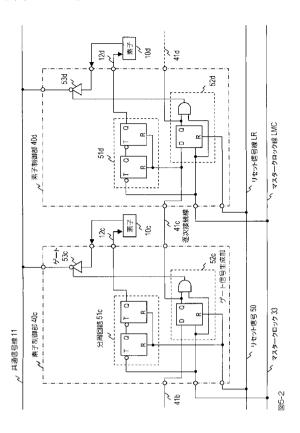

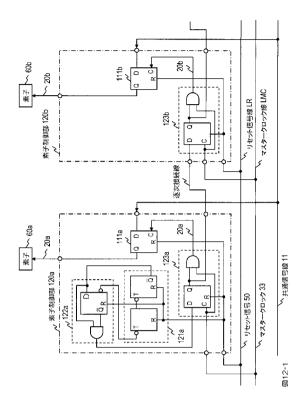

制御部を素子ごとに設けられる素子制御部とし、配線数も減らした実施例 2 を図 1 2 (作図上の都合により図 1 2 - 1 と図 1 2 - 2 に分かれているが、本来 1 個の物である)に示す。各素子 6 0 a , 6 0 b , 6 0 c , 6 0 d ごとに素子制御部 1 2 0 a , 1 2 0 b , 1 2 0 c , 1 2 0 d が設けられ、各素子 6 0 a ~ 6 0 d には、各素子制御部内に設けられた保持素子 1 1 1 a ~ 1 1 1 d で保持された信号が、供給されている。実施例 2 では、 1 1 1 a ~ 1 1 d を各素子制御部内に組み込んだ構成としている。動作は、信号多重化装置の実施例 2 で説明した図 5 の動作とほぼ同じである。

#### [0035]

そこで、対応するものの参照符号を明らかにすることで、動作説明は省略する。図5-1の初期化指示生成部42が図12の初期化指示生成部122、分周回路51が分周回路121、ゲート信号生成部52が保持信号生成部123に対応する。

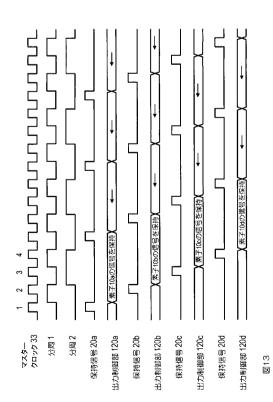

図12の多重分離装置の動作タイムチャートを図13に示す。素子制御部120a内の保持信号20aは、マスタークロック33のクロック1のタイミングで発生する。素子制御部120bが生成する保持信号20bは、マスタークロック33のクロック2のタイミングで発生する。以下同様に、素子60cの保持信号20cはクロック3、素子60dの保持信号はクロック4のタイミングで発生され、以降繰り返される。

## [0036]

図12の例では、保持素子111がDFFで構成されているので、保持信号の立下りの瞬間の共通信号線11上のディジタル信号を保持するように動作する。今、信号多重化装置もこの保持信号20aに対応するゲート信号13aをある特定の位置のマイクロホンからなる素子10aに割り当てたとすると、そのマイクロホンの位置で捕らえた音波を素子60aのスピーカーで再生することができる。

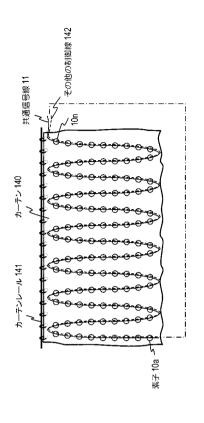

例えば、信号多重化装置の実施例3を応用した例を図14に示す。図14は、部屋の窓等に取り付けられるカーテン140にこの発明による信号多重化装置を組み込んだ例を示す。カーテンレール141に掛けられたカーテン140の表面全体にマイクロホンからなる素子10a~10nが多数分散配置されていて、それらの素子間が共通信号線11で結ばれている。共通信号線11に沿って破線で示すその他の制御線142が配線されている。その他の制御線142は、例えば各素子に電源を供給する電源線と、初期化する為のリセット信号と、マスタークロックからなる。

### [0037]

信号多重化装置側をこのカーテン140のように構成し、多重信号分離装置側を、図示しないが、図14の素子をスピーカーに置き換えた同じカーテン状のものとする。そうした上で信号多重化装置側の素子10aの位置で収音した音波を、再生するスピーカー(素子60a)をカーテン上の同じ位置に相当する場所に素子60aを置く。そうしておいて、そのカーテン状の多重信号分離装置を他の部屋の窓に掛け、両方のカーテンを共通信号線で結ぶと、信号多重化装置側が置かれた部屋の音場を他の部屋に忠実に伝達することが可能である。

10

20

30

#### [0038]

図14を参照して説明した信号多重化装置と多重信号分離装置において共通する点は、多くの素子が分布して設けられ、これら素子の配置に沿って共通信号線11及びその他の制御線142が設けられ、共通信号線上における時分割多重化信号には同期信号が含まれないものである。共通信号線11やその他の制御線142は、一次元のみならず図14に示したようにほぼ2次元に配置してもよく、或いは、図4で述べたように図14中に一点鎖線で示すように共通信号線11及びその他の制御線142の始端と終端を連結して環状に接続してもよい。この場合は図5、図12に示した実施例では終端の素子制御部からの逐次接続線を、始端の素子制御部のゲート信号生成部に初期化指示生成部42からの信号の替わりに接続すればよい。この場合は、マスタークロック33の周波数をオーバーサンプリング周波数の調度素子数倍にする必要がある。

10

#### 「実施例31

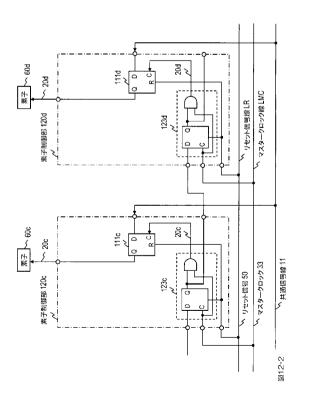

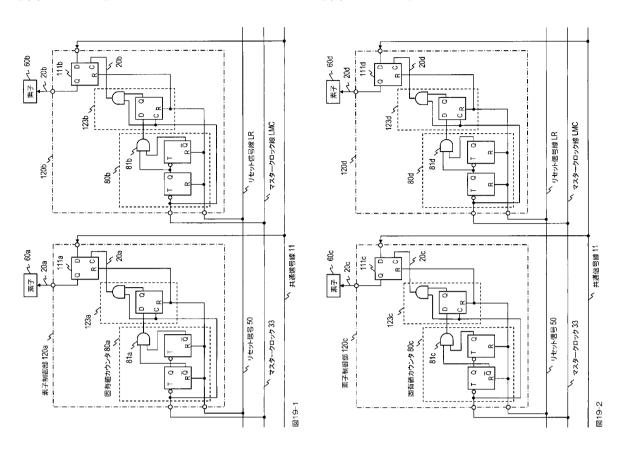

多重信号分離装置も実施例 2 に示した逐次接続線を無くすことが可能である。逐次接続線を無くした実施例 3 を図 1 9 (作図上の都合により図 1 9 - 1 と図 1 9 - 2 に分かれているが、本来 1 個の物である)に示す。上記した多重信号分離装置の実施例 2 (図 1 2)の各素子制御部内に、信号多重化装置の実施例 3 (図 8)で示したものと同じように、固有値カウンタ 8 0 a ~ 8 0 dを設けたものである。参照符号を同一とし動作説明は省略する。このように多重信号分離装置においても実施例 2 に示した各素子制御部内の分周回路を、固有値カウンタに置き換えることで、逐次接続線が必要でなくなる。

20

## [0039]

その結果、共通信号線11とリセット信号線LRとマスタークロック線LMCの3本の配線だけで、n個の素子の信号を多重信号分離することができる。

以上述べたような構成において、オーバーサンプル低振幅分解能符号化によってディジタル化された信号が時分割多重化されて伝送される共通信号線上のディジタル信号を、オーバーサンプリングの1周期ごとに保持する過程により共通信号線上の信号を分離する多重信号分離方法が実現できる。

以上、この発明による信号多重化装置と多重信号分離装置を、マイクロホンとスピーカーとからなる素子の例で説明を行って来たが、この発明は、これに限定されない。図 1 5 に示すように他のセンサを用いることも可能である。

30

## [0040]

図15(a)は、マイクロホンの代わりに温度センサを用いた素子を示している。温度センサ150を図14に示したように多数分散させて配置することで、部屋や比較的大きな物体の温度分布を細かく把握することが可能になる。室内温度は音ほど変化の速度が速く無いので、敢えてオーバーサンプリングで動作させる必要は無いが、この発明の特徴である少ない信号線で多数の情報を伝達できる特徴を生かすことが出来る。

図15(b)はマイクロホンの替りに加速度センサ151を用いた素子を示している。 ロボット等には、多数の3軸の加速度センサが用いられる。そのような複数の情報を多数 伝送する場合には、共通信号線を増やすことで対応可能である。単純に共通信号線の数を 増やすことで、例えばロボット等の制御にこの発明を応用することもできる。

40

#### [0041]

他のセンサの利用も考えられる。例えばペーハー(PH)センサを用い、河川の環境測定をするような場合にもこの発明が利用可能である。その場合はマスタークロックが数 Kmに渡って配線されることが考えられるので、遅延及び損失の少ない光ファイバーケーブルでマスタークロックを伝送する等の工夫は必要になる。しかし、そのような用途においても、この発明の技術思想はそのまま生かすことが可能である。

以上のようにこの発明の信号多重化装置及び多重信号分離装置によれば、伝送系の信号線をオーバーサンプル低振幅符号化ディジタル信号の少ない信号線(1~数bitの共通信号線)だけで形成でき、個々の伝送信号に識別信号を必要としない、低コストで高速な時分割多重伝送が実現できる。

[0042]

なお、上記した実施例では、1 bit A / D 変換及び1bit 復号器の例で説明を行って来たが、オーバーサンプル低振幅分解能符号化技術による A D 変換器及び復号器は3 bit 程度まで多bit 化できることが周知である。振幅精度が求められるような場合は、2 bit あるいは3 bit 化する場合も想定される。その場合は、上記説明した1 bit A / D 変換器と復号手段を単純に多bit 化し、それぞれのbit に対して共通信号線を設ければ同じようにこの発明が実現可能である。

また、この発明の信号多重化装置の実施例 1 ~ 3 と、多重信号分離装置の実施例 1 ~ 3 とは、相互に独立した関係で組み合わせることが可能であり、どのように組み合わせてもこの発明の特徴である、構成が簡単で、伝送系の信号線の数が最小で、また高速である効果を得ることが出来る。

【図面の簡単な説明】

[0043]

- 【図1】この発明による信号多重化装置の実施例1の機能構成例を示す図。

- 【図2】図1中の素子の一例(マイクロホン)を示す図。

- 【図3】図1中の制御部100の動作タイムチャートを示す図。

- 【図4】この発明による信号多重化装置の実施例2の機能構成例を示す図。

- 【図5-1】この発明による信号多重化装置の実施例2の具体構成例を示す図。

- 【図5-2】この発明による信号多重化装置の実施例2の具体構成例を示す図。

- 【図6】図5-1と図5-2の動作タイムチャートを示す図。

- 【図7】この発明による信号多重化装置の実施例3の機能構成例を示す図。

- 【図8-1】この発明による信号多重化装置の実施例3の具体的構成例を示す図。

- 【図8-2】この発明による信号多重化装置の実施例3の具体的構成例を示す図。

- 【図9】図8-1と図8-2の動作タイムチャートを示す図。

- 【図10】この発明による多重信号分離装置の実施例1の機能構成例を示す図。

- 【図11】図10中の素子の一例(スピーカー)を示す図。

- 【図12-1】この発明による多重信号分離装置の実施例2の機能構成例を示す図。

- 【図12-2】この発明による多重信号分離装置の実施例2の機能構成例を示す図。

- 【図13】図12の動作タイムチャートを示す図。

- 【図14】この発明の信号多重化装置又は多重信号分離装置の適用例を示す図。

- 【図15】他の素子の例を示す図。

- 【図16】従来のオーバーサンプル低振幅符号化技術による1bit AD変換器の例を示す図。

- 【図17】従来のオーバーサンプル1bit復号化手段を示す図。

- 【図18】従来の多チャネル符号化装置を示す図。

- 【図19-1】この発明による多重信号分離装置の実施例3の具体的構成例を示す図。

- 【図19-2】この発明による多重信号分離装置の実施例3の具体的構成例を示す図。

10

20

【図1】 【図2】

【図3】 【図4】

【図5-1】

【図5-2】

【図6】

【図7】

【図8-1】

【図8-2】

【図9】

【図10】

【図11】

【図12-1】

【図12-2】

【図13】

【図14】

22a

【図16】

【図18】

【図17】

【図19-1】

【図19-2】

### フロントページの続き

## (72)発明者 鎌本 優

東京都千代田区大手町二丁目 3 番 1 号 日本電信電話株式会社内

## (72)発明者 松谷 康之

東京都千代田区大手町二丁目3番1号 日本電信電話株式会社内

## 審査官 白井 亮

## (56)参考文献 特開平09-223971 (JP,A)

特開平10-145232(JP,A)

特開2005-057467(JP,A)

特開2004-191545(JP,A)

特開昭59-200554(JP,A)

特開2003-196230(JP,A)

## (58)調査した分野(Int.CI., DB名)

H04J 3/00-3/26

H04L 5/22-5/26